REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

MINISTERE DE L'ENSEIGNEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE

UNIVERSITE MENTOURI CONSTANTINE

FACULTE DES SCIENCES DE L'INGENIEUR

DEPARTEMENT D'ELECTRONIQUE

**POLYCOPIE DE COURS**

**TRAVAUX DIRIGES ET TRAVAUX PRATIQUES**

T. LAROUSSI

M. T. BENHABILLES

A. FARROUKI

**MICROPROCESSEUR INTEL 8086 ET SES PERIPHERIQUES**

**ARCHITECTURE ET PROGRAMMATION**

**ANNEE UNIVERSITAIRE 2009-2010**

# TABLE DES MATIERES

## CHAPITRE 1 MACHINES ALGORITHMIQUES

|      |                                                                               |    |

|------|-------------------------------------------------------------------------------|----|

| I    | Introduction                                                                  | 1  |

| II   | Notion d'automate fini                                                        | 1  |

| III  | Matérialisation de la primitive de calcul par un circuit logique combinatoire | 2  |

| IV   | Modèle de Glushkov                                                            | 3  |

| IV.1 | Unité de traitement                                                           | 3  |

| IV.2 | Unité de commande                                                             | 4  |

| V    | Microprocesseur                                                               | 6  |

| VI   | Appel de sous-programme                                                       | 9  |

| VI.1 | Mémoire FILO utilisée comme pile de programme                                 | 10 |

| VII  | Exemple d'application                                                         | 11 |

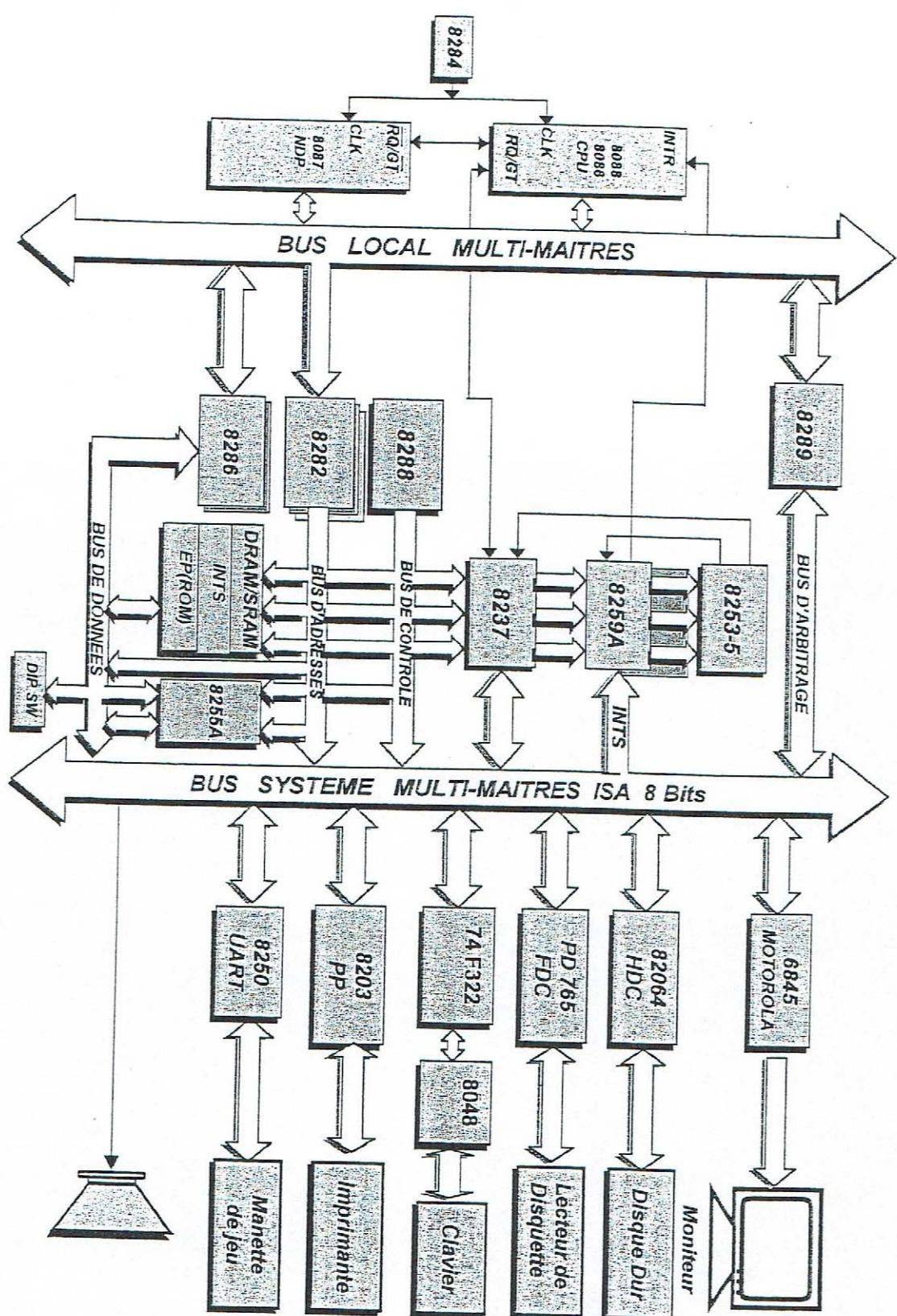

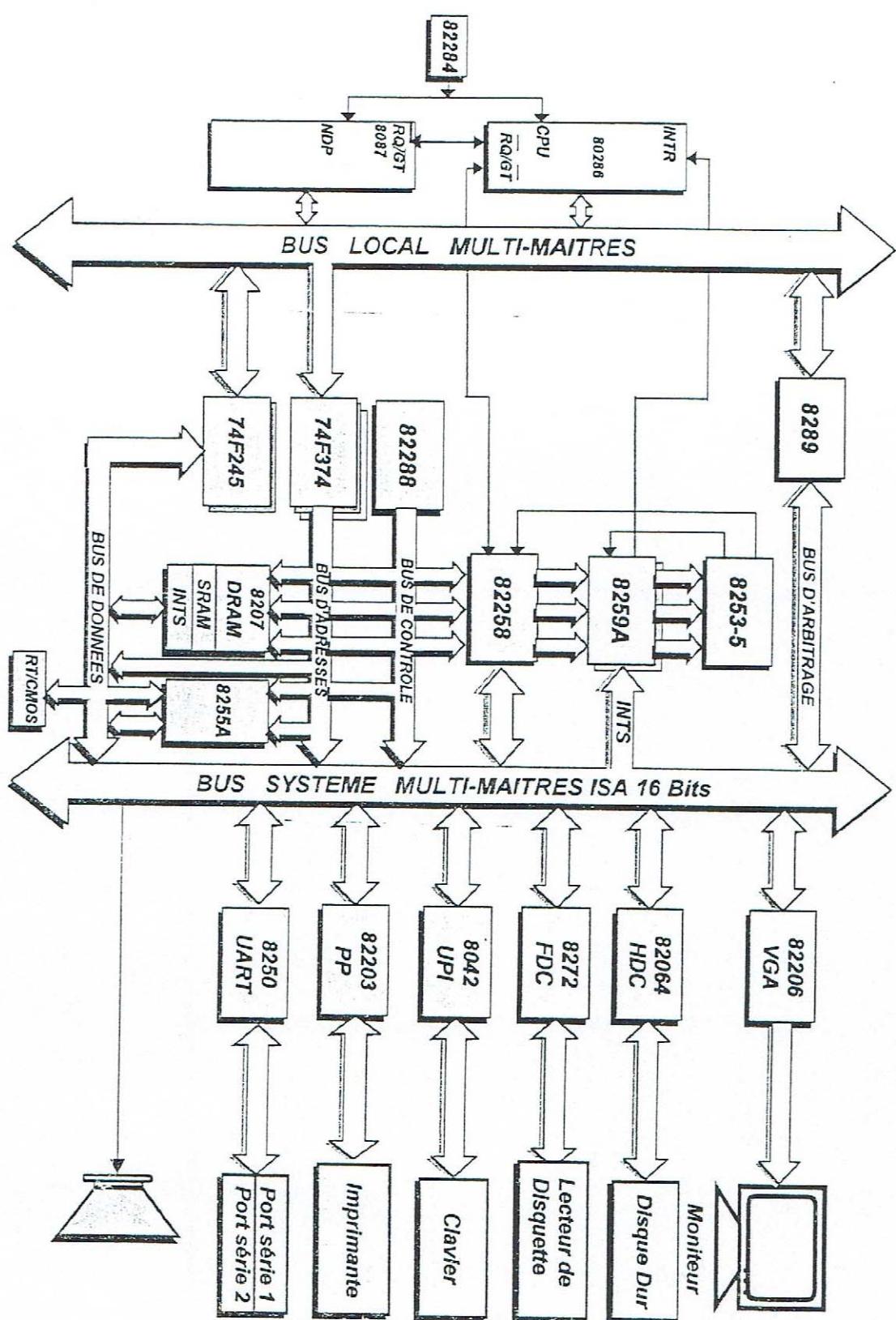

## CHAPITRE 2 MICRO-ORDINATEUR IBM PC-XT

|       |                                                  |    |

|-------|--------------------------------------------------|----|

| I     | Introduction                                     | 12 |

| II    | Circuit de la carte mère                         | 12 |

| II.1  | Microprocesseur                                  | 12 |

| II.2  | Coprocesseur mathématique                        | 12 |

| II.3  | Buffer de données bidirectionnel 8286/8287       | 13 |

| II.4  | Latch d'adresses 8282                            | 13 |

| II.5  | Contrôleur de bus 8288                           | 13 |

| II.6  | Circuit d'horloge 8284                           | 13 |

| II.7  | Contrôleur d'accès direct mémoire DMAC 8237      | 13 |

| II.8  | Contrôleur d'interruptions programmable PIC 8259 | 14 |

| II.9  | Temporisateur-compteur programmable CTC 8253     | 14 |

| II.10 | Interface parallèle de périphérique PPI 8255     | 14 |

| II.11 | Mémoire centrale                                 | 15 |

| II.12 | Indicateurs de configuration matérielle          | 15 |

| III   | Cartes d'extensions                              | 16 |

| III.1 | Carte graphique                                  | 17 |

| III.2 | Contrôleur de lecteurs de disquettes FDC 8272    | 17 |

| III.3 | Port série et le port parallèle                  | 17 |

| III.4 | Clavier                                          | 17 |

|                                                |    |

|------------------------------------------------|----|

| III.5 Connecteurs du bus ou slots d'extensions | 18 |

| IV Alimentation                                | 18 |

## **CHAPITRE 3**

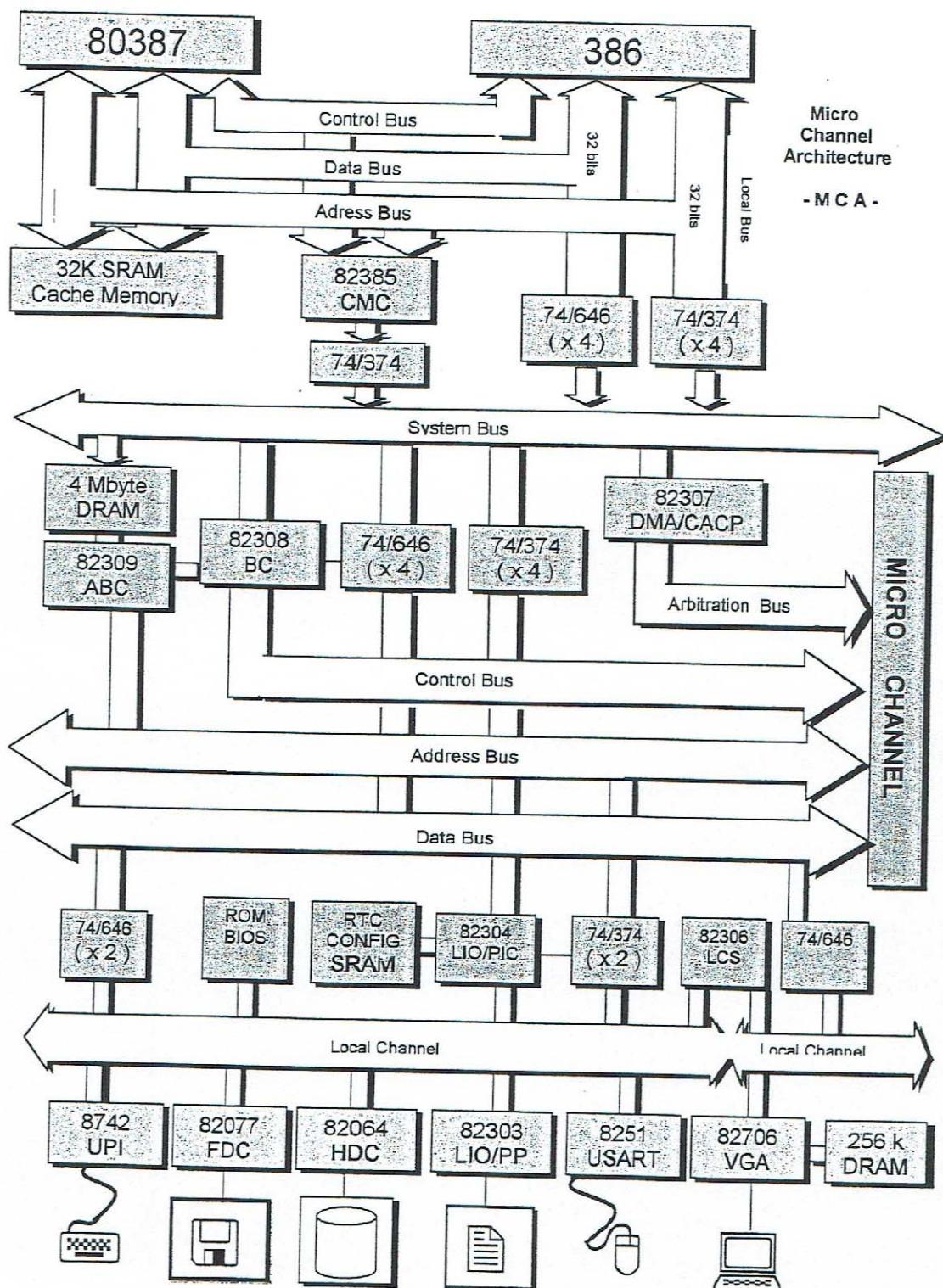

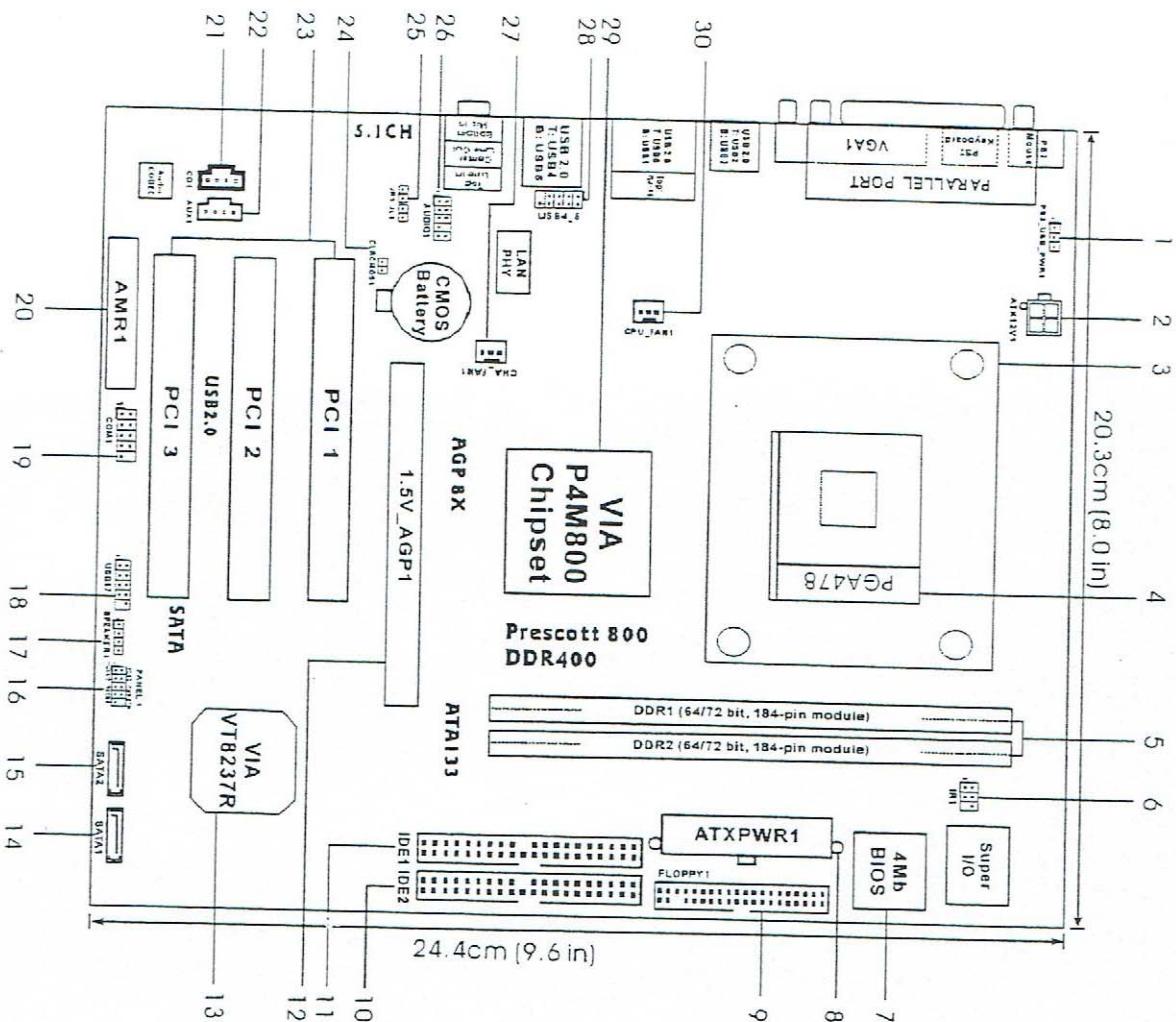

### **EVOLUTION DES MICRO-ORDINATEURS PC**

21

|                                                     |    |

|-----------------------------------------------------|----|

| I Introduction                                      | 21 |

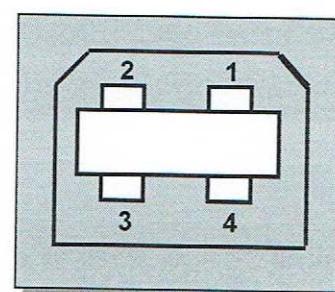

| II Bus                                              | 22 |

| II.1 Anciens bus                                    | 22 |

| II.2 Nouveaux bus                                   | 23 |

| III Evolution des iAPX86                            | 24 |

| III.1 Microprocesseurs                              | 25 |

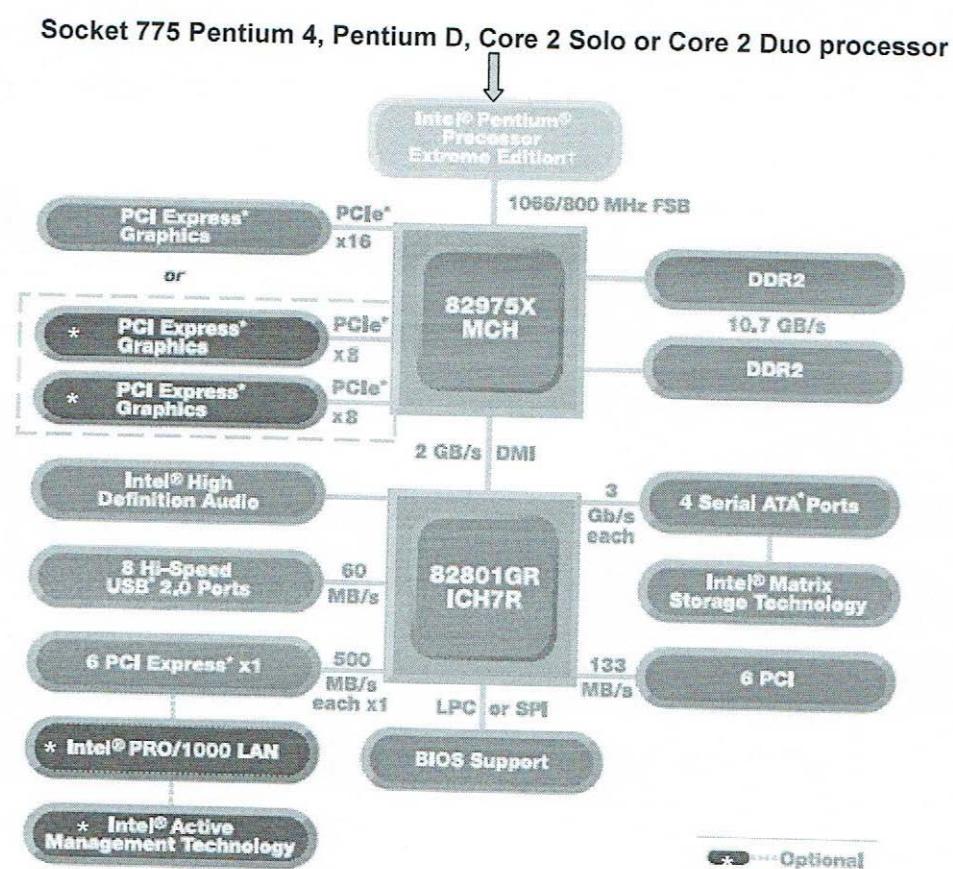

| III.2 Chipsets ou jeux de composants                | 26 |

| IV Mémoires                                         | 28 |

| V Connecteurs ou interfaces disques durs            | 30 |

| VI Affichage graphique                              | 32 |

| VI.1 Cartes et modes graphiques                     | 32 |

| VI.2 Affichage haute définition                     | 33 |

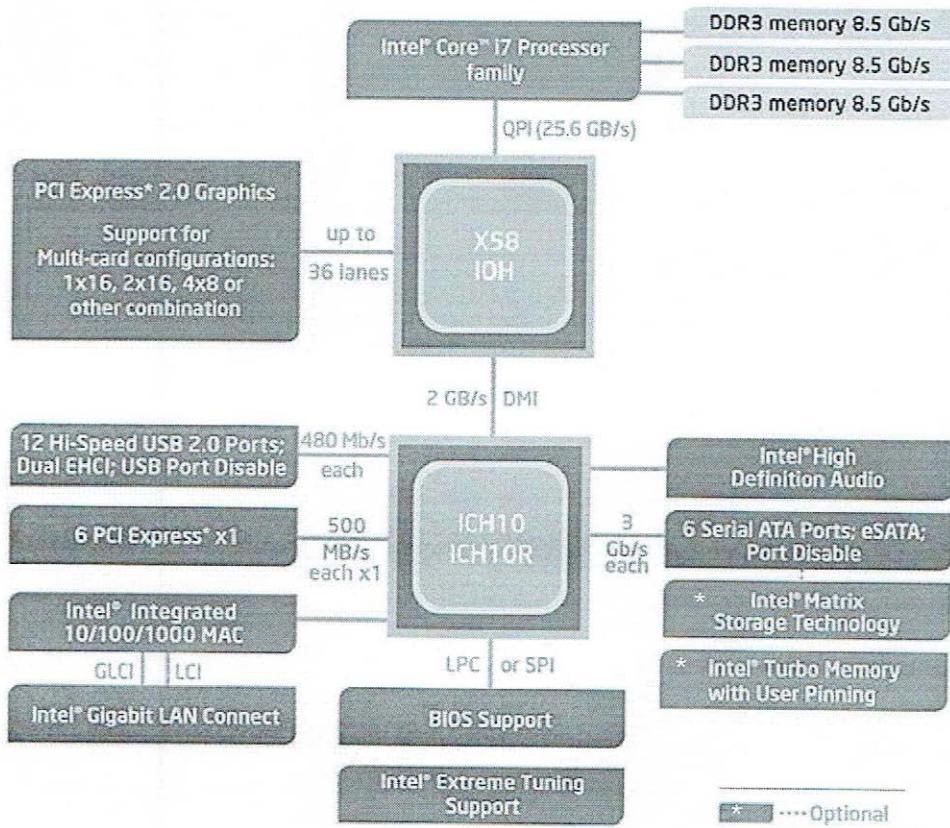

| VII Synoptique d'une carte mère dernière génération | 34 |

## **CHAPITRE 4**

### **ARCHITECTURE DU 8086**

35

|                                                                   |    |

|-------------------------------------------------------------------|----|

| I Introduction                                                    | 35 |

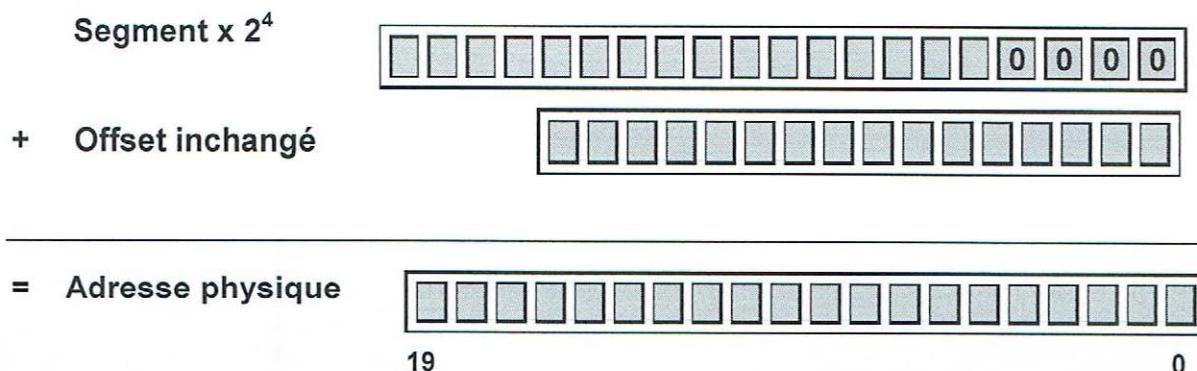

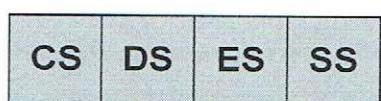

| II Principe de la segmentation                                    | 35 |

| II.1 Quelques définitions                                         | 35 |

| III Architecture du 8086                                          | 37 |

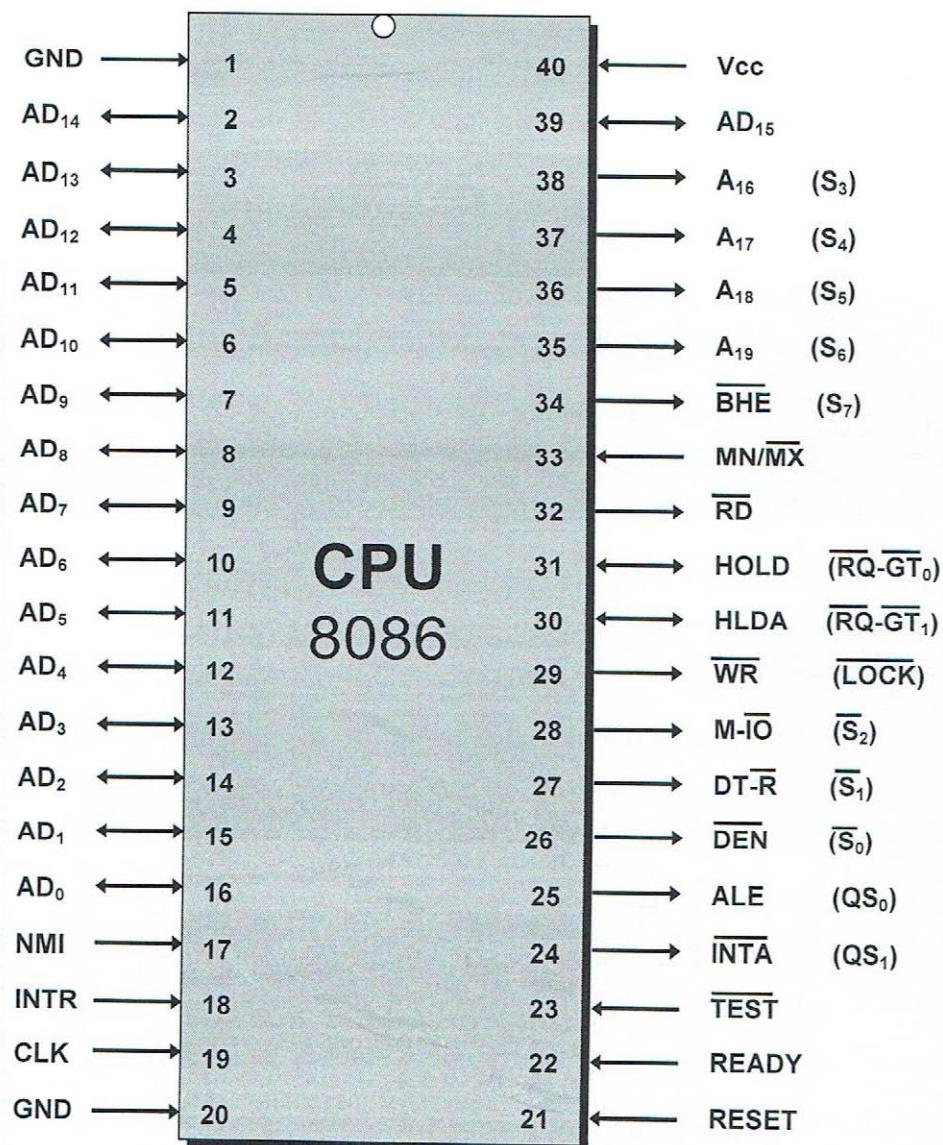

| III.1 Architecture externe                                        | 37 |

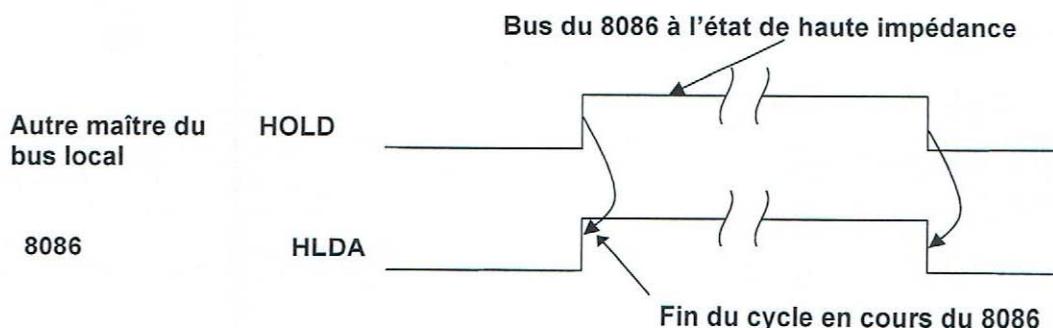

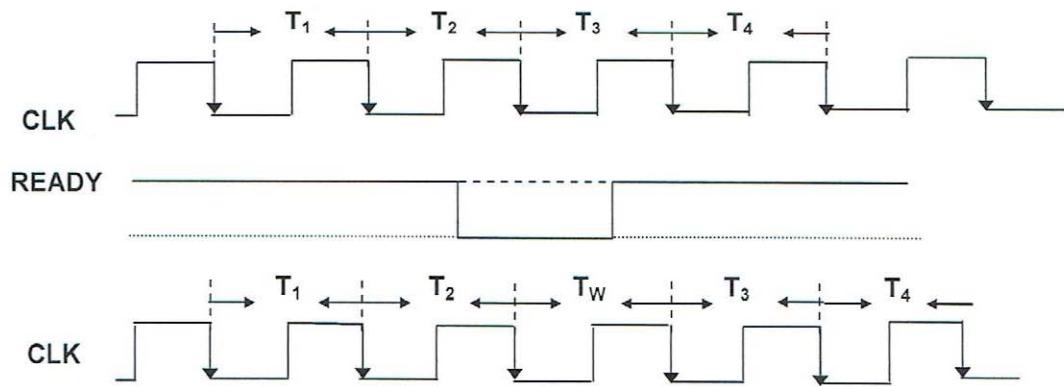

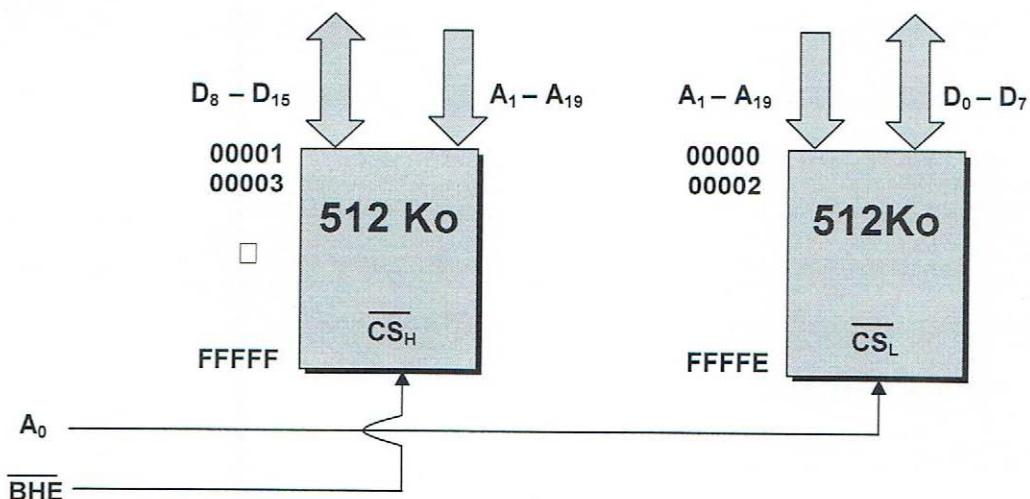

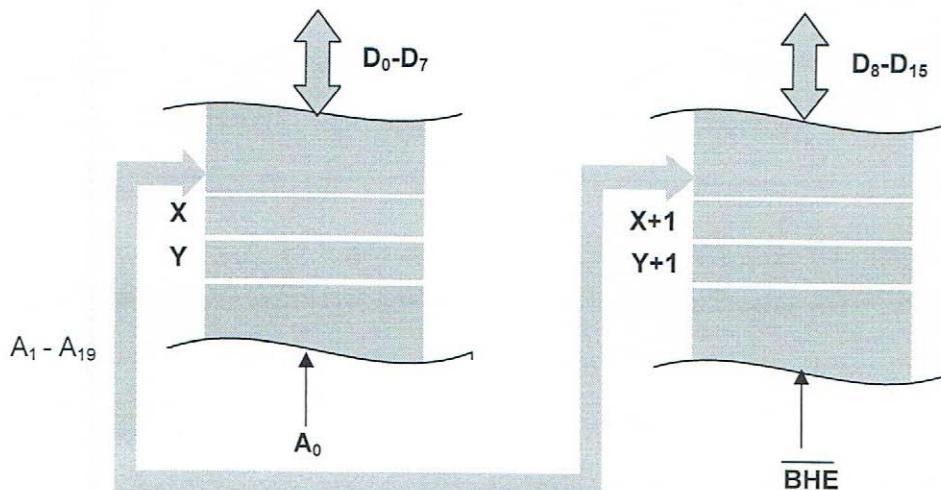

| III.2 Chronogrammes de Lecture/Ecriture dans le 8086              | 44 |

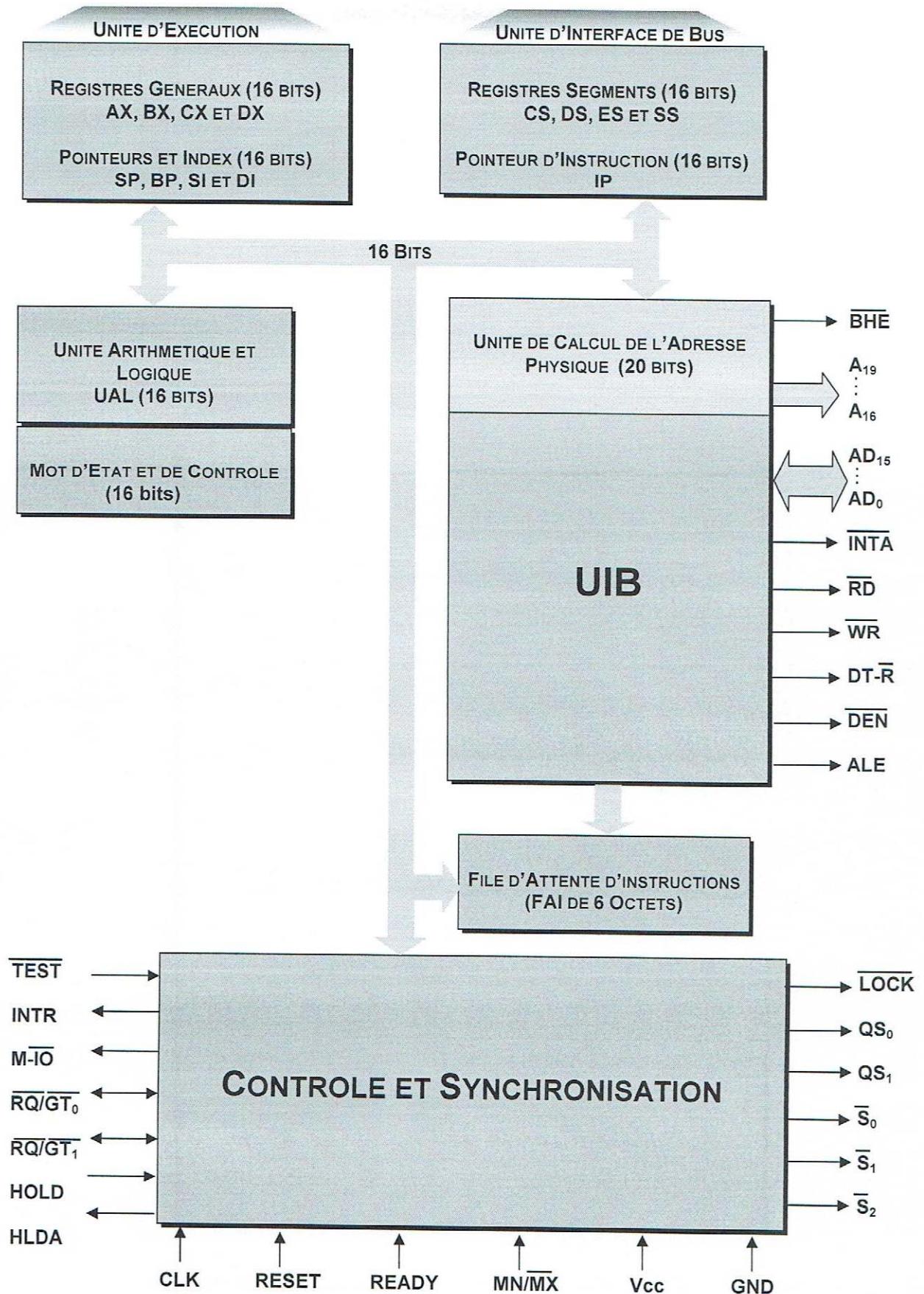

| III.3 Architecture interne du 8086                                | 48 |

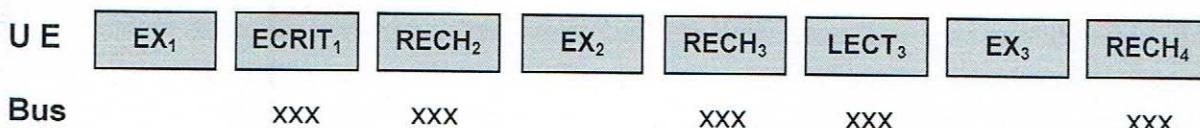

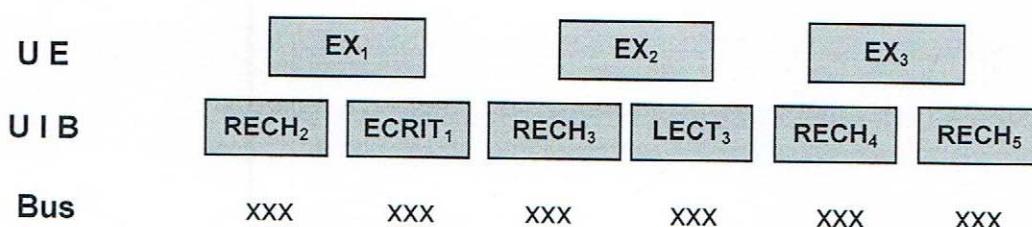

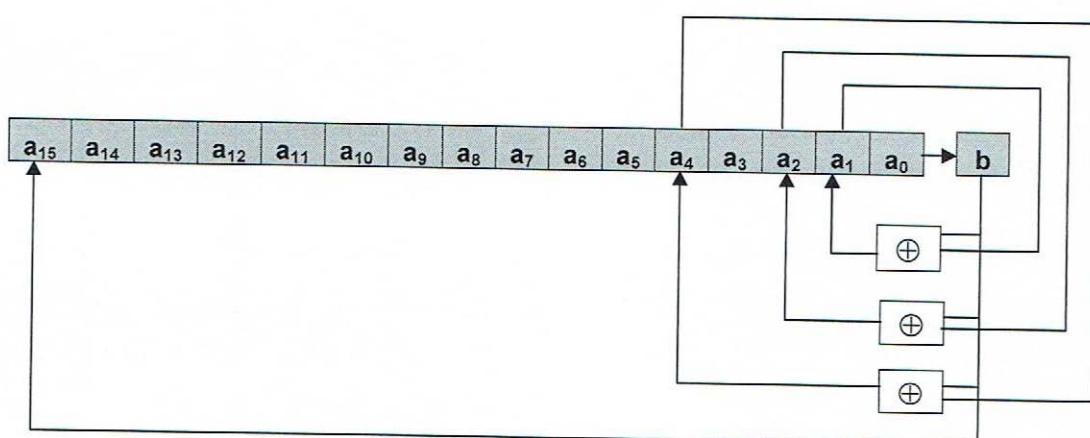

| IV Concept de la pré-recherche (prefetch)                         | 54 |

| V.1 Microprocesseur de la 2ème génération                         | 54 |

| V.2 Microprocesseur avec file d'attente d'instructions (prefetch) | 54 |

## **CHAPITRE 5**

### **ASSEMBLEUR DU 8086**

56

|                                                             |    |

|-------------------------------------------------------------|----|

| I Introduction                                              | 56 |

| II Jeu d'instructions du 8086                               | 56 |

| II.1 Instructions de transferts de données                  | 56 |

| II.2 Instructions arithmétiques                             | 58 |

| II.3 Instructions logiques                                  | 60 |

| II.4 Instructions de manipulation des chaînes de caractères | 61 |

| II.5 Instructions de branchements                           | 62 |

| II.6 Instructions de contrôle du 8086                       | 69 |

| III Modes d'adressages dans le 8086                         | 70 |

| III.1 Mode d'adressage immédiat                             | 70 |

| III.2 Mode d'adressage direct                               | 70 |

|                                                     |    |

|-----------------------------------------------------|----|

| III.3 Mode d'adressage basé                         | 71 |

| III.4 Mode d'adressage indexé                       | 71 |

| III.5 Mode d'adressage indexé et basé               | 72 |

| III.6 Mode d'adressage basé et déplacement          | 72 |

| III.7 Mode d'adressage indexé et déplacement        | 73 |

| III.8 Mode d'adressage basé, indexé et déplacement  | 73 |

| III.9 Mode d'adressage registre-registre            | 74 |

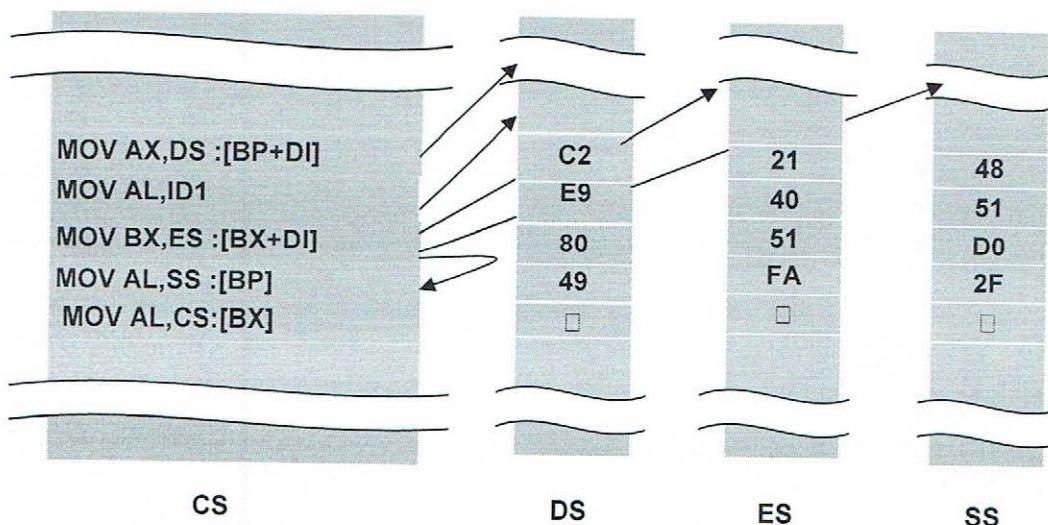

| IV Accès à des segments multiples: Segment Override | 74 |

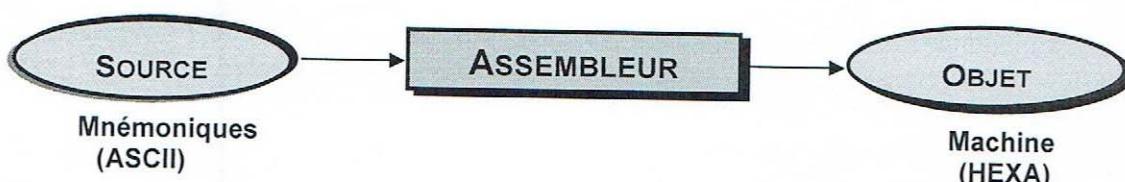

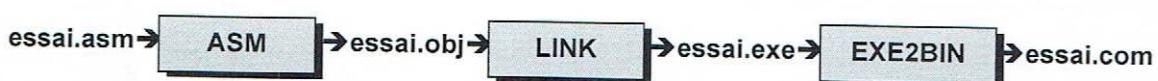

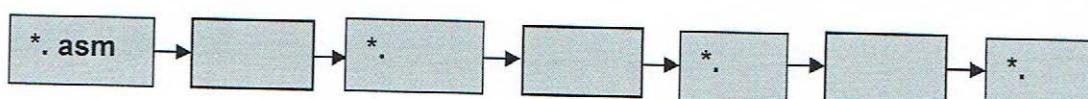

| V Assembleur du 8086                                | 75 |

| V.1 Définitions                                     | 75 |

| V.2 Exemples d'assembleurs                          | 76 |

| VI Structure d'une ligne assembleur                 | 78 |

| VII Exemples de programmation du 8086               | 78 |

| VII.1 Premier exemple                               | 78 |

| VII.2 Deuxième exemple                              | 80 |

## CHAPITRE 6

### ORGANISATION LOGICIELLE DANS LE 8086

83

|                                                     |    |

|-----------------------------------------------------|----|

| I Introduction                                      | 83 |

| II Organisation minimale                            | 83 |

| III Organisation structurée                         | 83 |

| IV Modules multiples                                | 84 |

| V Regroupement                                      | 84 |

| V.1 Groupe                                          | 84 |

| V.2 Classe                                          | 84 |

| VI Structure d'un programme                         | 85 |

| VI.1 Lien entre modules                             | 85 |

| VI.2 Segment                                        | 87 |

| VI.3 Compteur d'emplacements ou compteur d'adresses | 87 |

| VI.4 Pseudo-instructions ou directives d'assemblage | 87 |

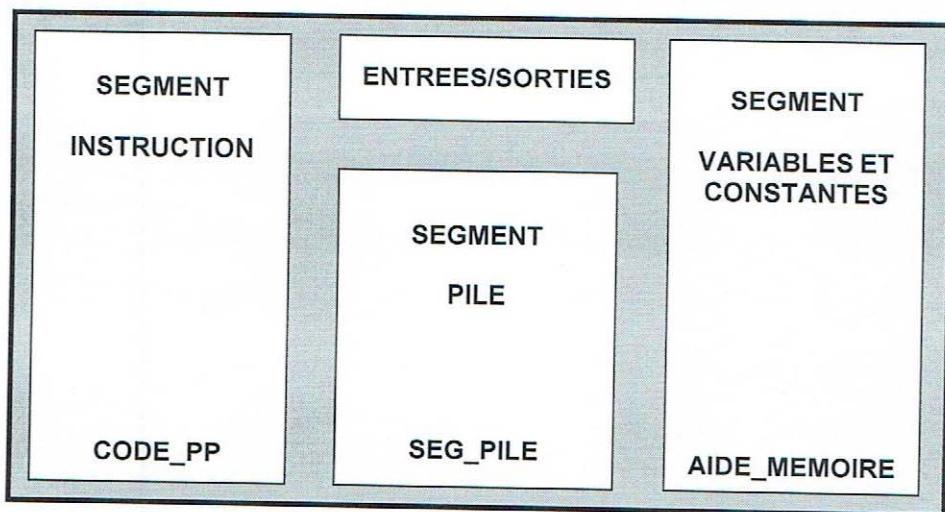

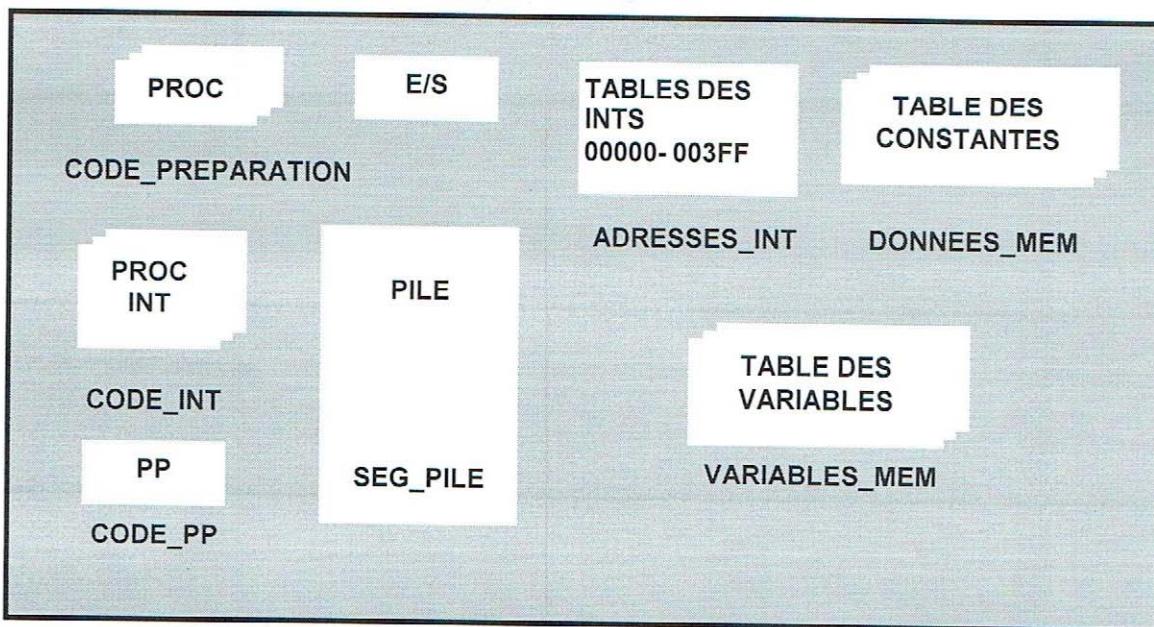

| VII Canevas d'écriture d'un programme               | 94 |

| VII.1 Première manière d'écrire un programme        | 94 |

| VII.2 Deuxième manière d'écrire un programme        | 95 |

## CHAPITRE 7

### MODES DE TRANSFERTS DES ENTREES ET SORTIES

98

|                                                   |     |

|---------------------------------------------------|-----|

| I Introduction                                    | 98  |

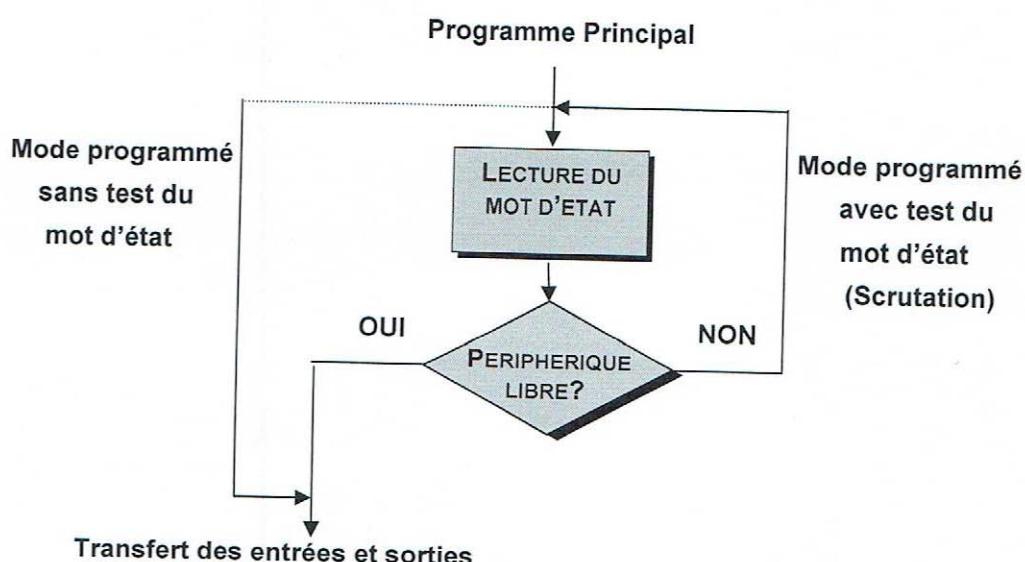

| II Mode programmé avec ou sans test du mot d'état | 98  |

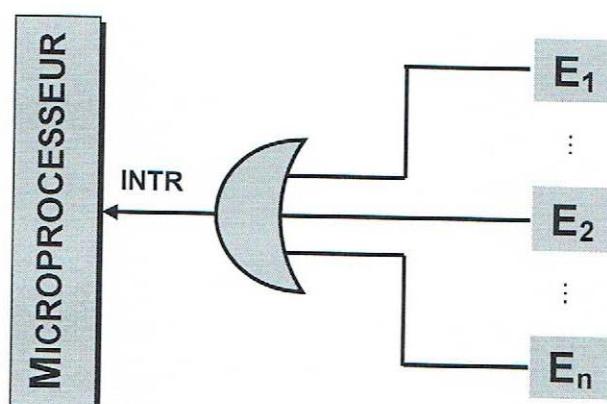

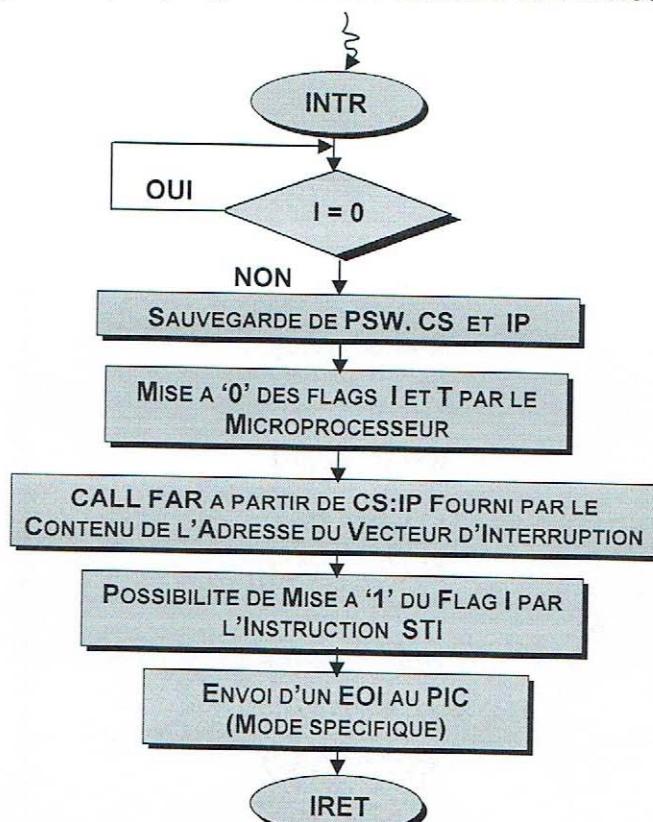

| III Mode interruptible                            | 99  |

| III.1 Définition                                  | 99  |

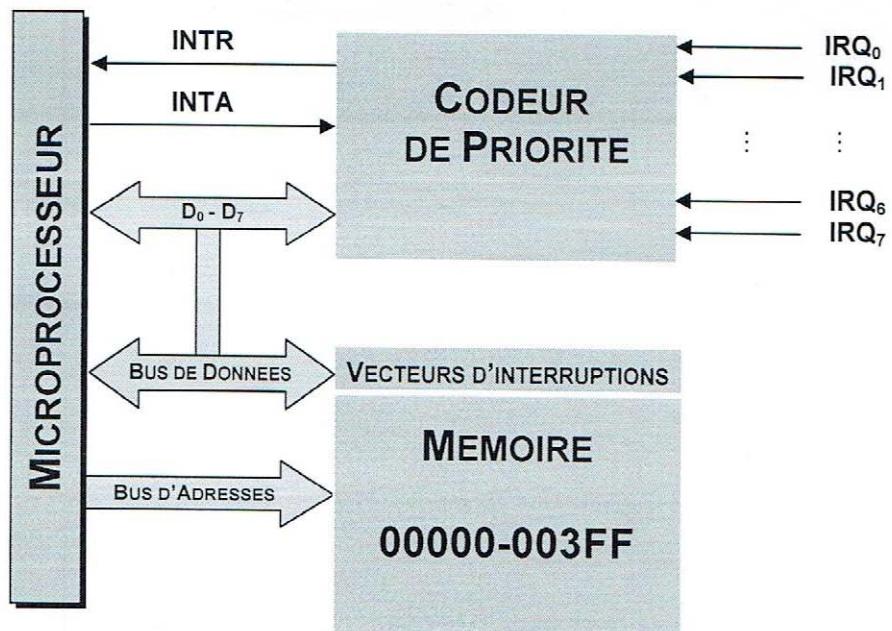

| III.2 Concept des interruptions                   | 99  |

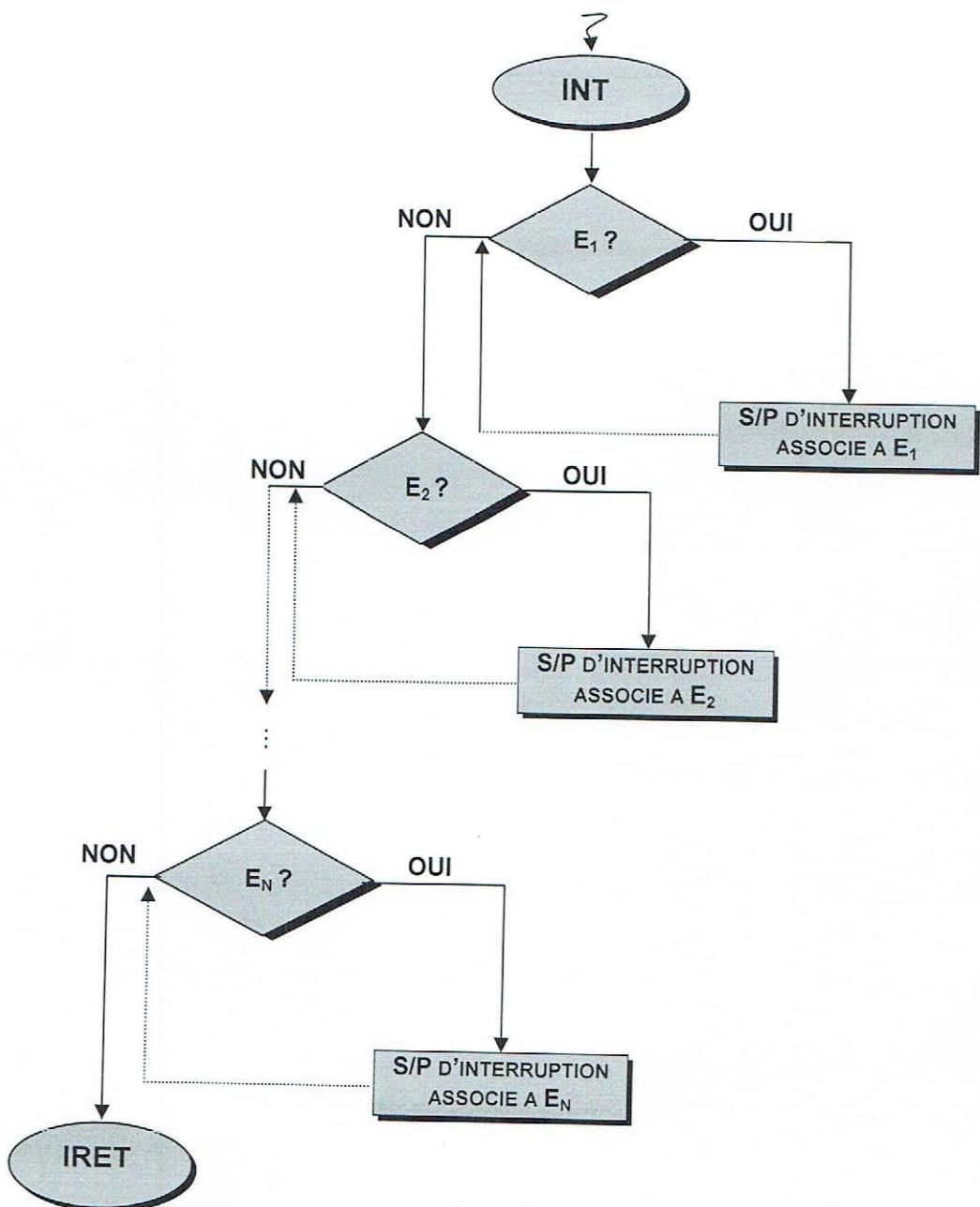

| III.3 Gestion des priorités                       | 100 |

| IV Mode DMA (Direct Memory Access)                | 102 |

| V Tableau récapitulatif                           | 104 |

|                                                                  |     |

|------------------------------------------------------------------|-----|

| <b>CHAPITRE 8</b>                                                |     |

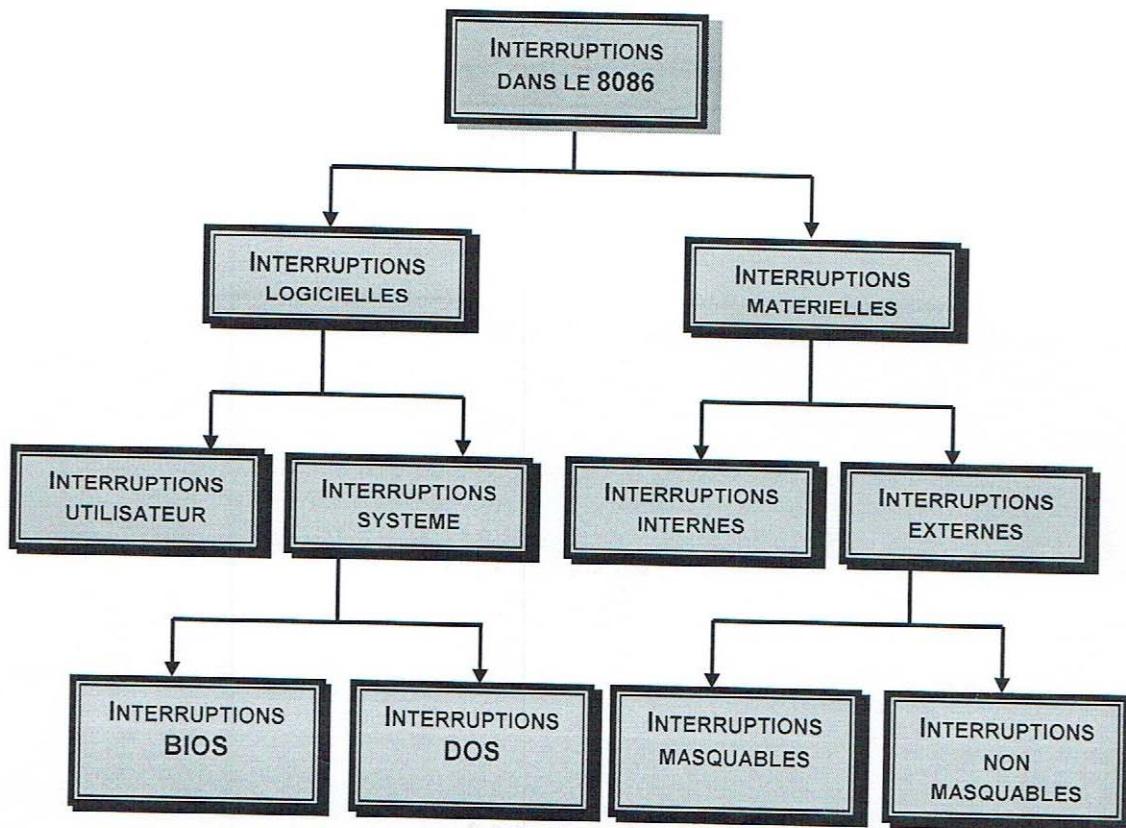

| <b>INTERRUPTIONS DANS LE 8086</b>                                | 105 |

| I Introduction                                                   | 105 |

| II Principe général des interruptions                            | 105 |

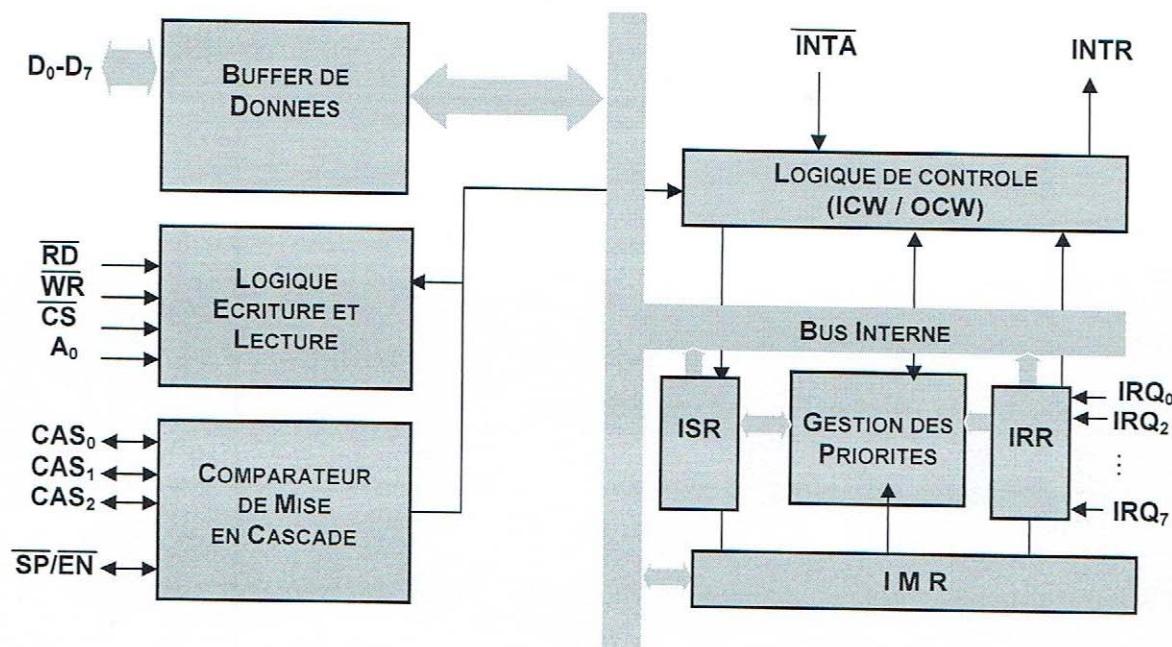

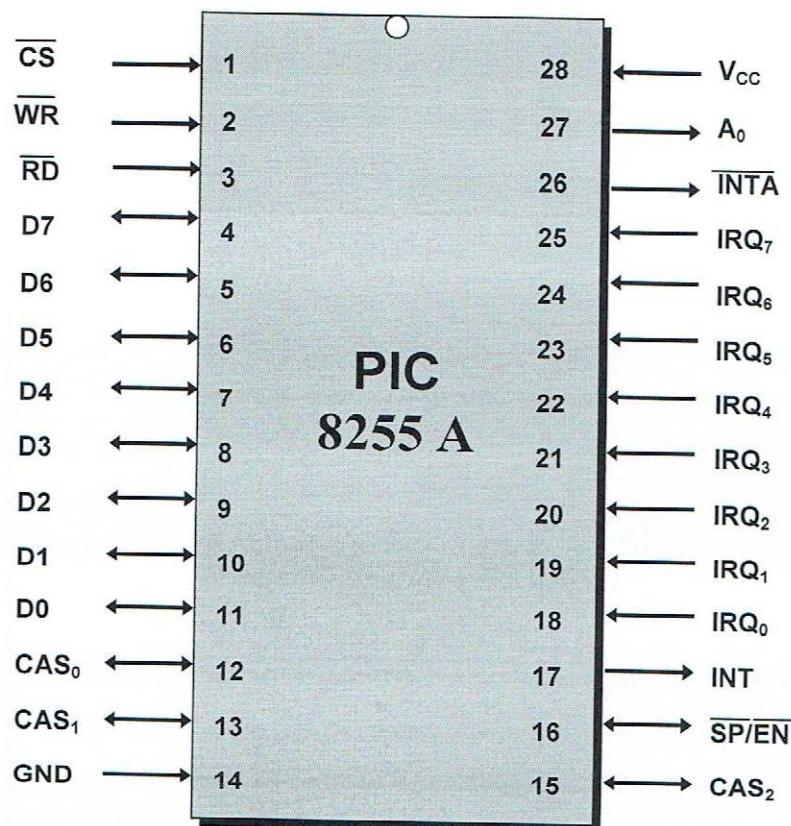

| III Description sommaire du contrôleur des interruptions         | 105 |

| III.1 Architecture Interne du PIC                                | 106 |

| III.2 Architecture Externe du PIC                                | 114 |

| IV Interruptions dans les PC                                     | 119 |

| IV.1 Interruptions matérielles                                   | 120 |

| IV.2 Interruptions logicielles                                   | 122 |

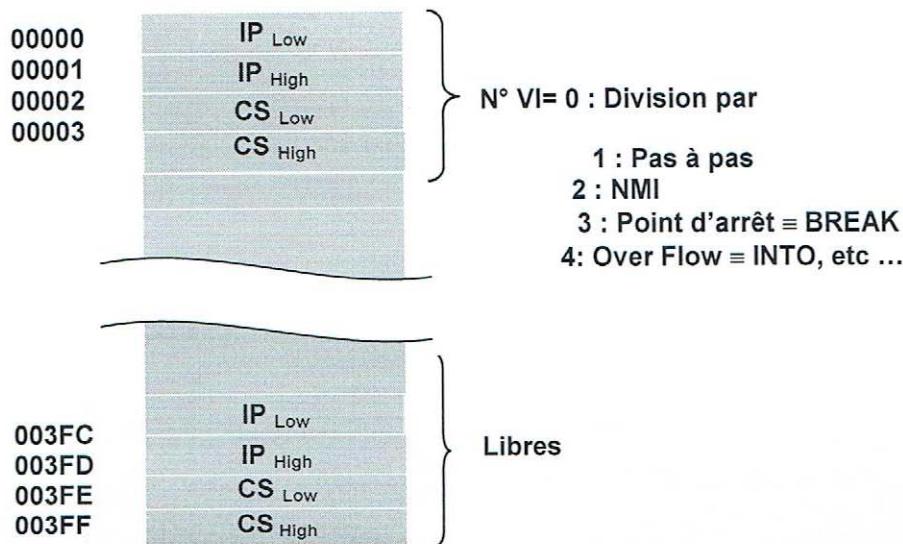

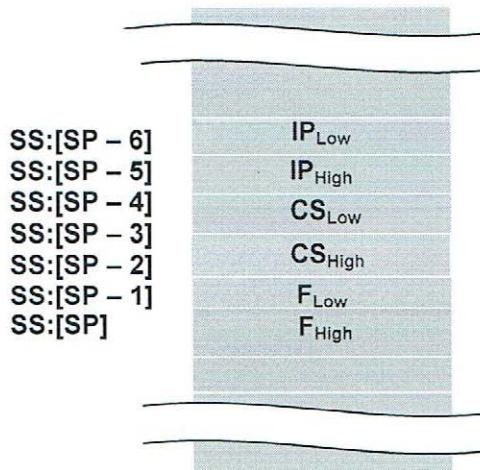

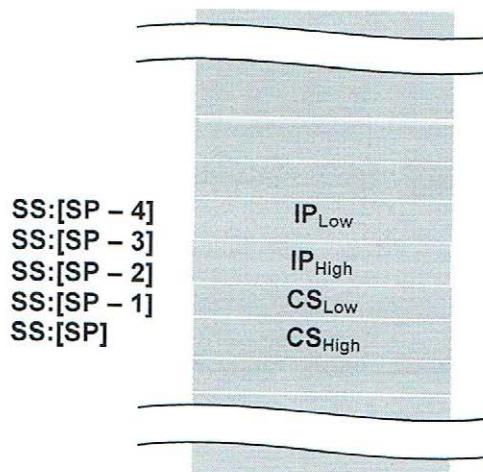

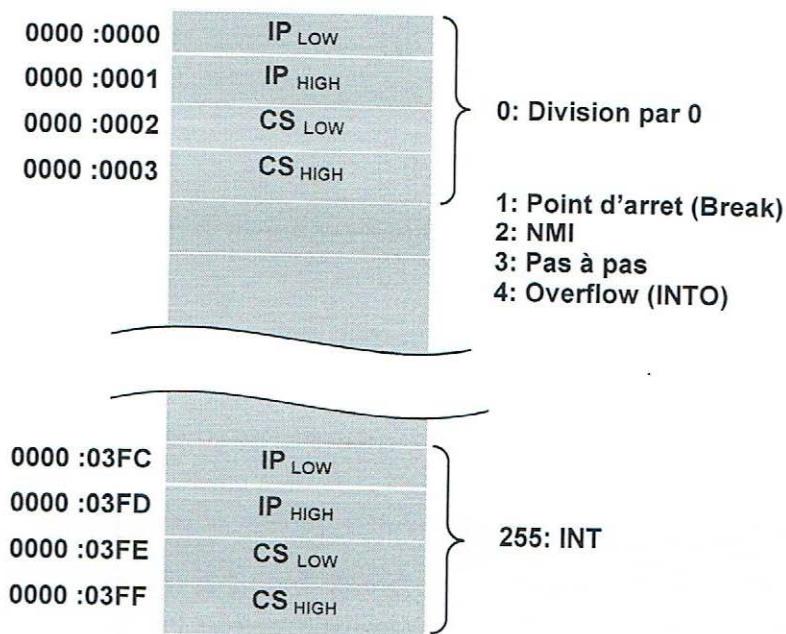

| IV.3 Vectorisation des interruptions                             | 123 |

| IV.4 Exemples d'applications des interruptions                   | 124 |

| <b>CHAPITRE 9</b>                                                |     |

| <b>CIRCUIT D'ENTREES ET DE SORTIES PARALLELE ET PROGRAMMABLE</b> | 128 |

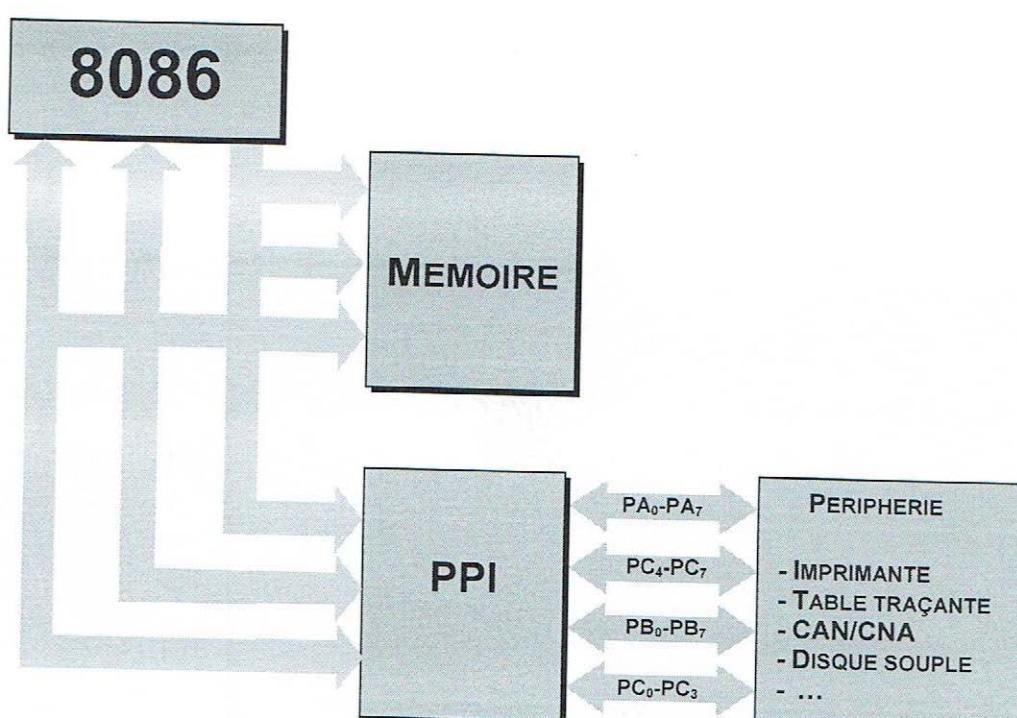

| I Introduction                                                   | 128 |

| II PPI (Programmable Peripheral Interface)                       | 128 |

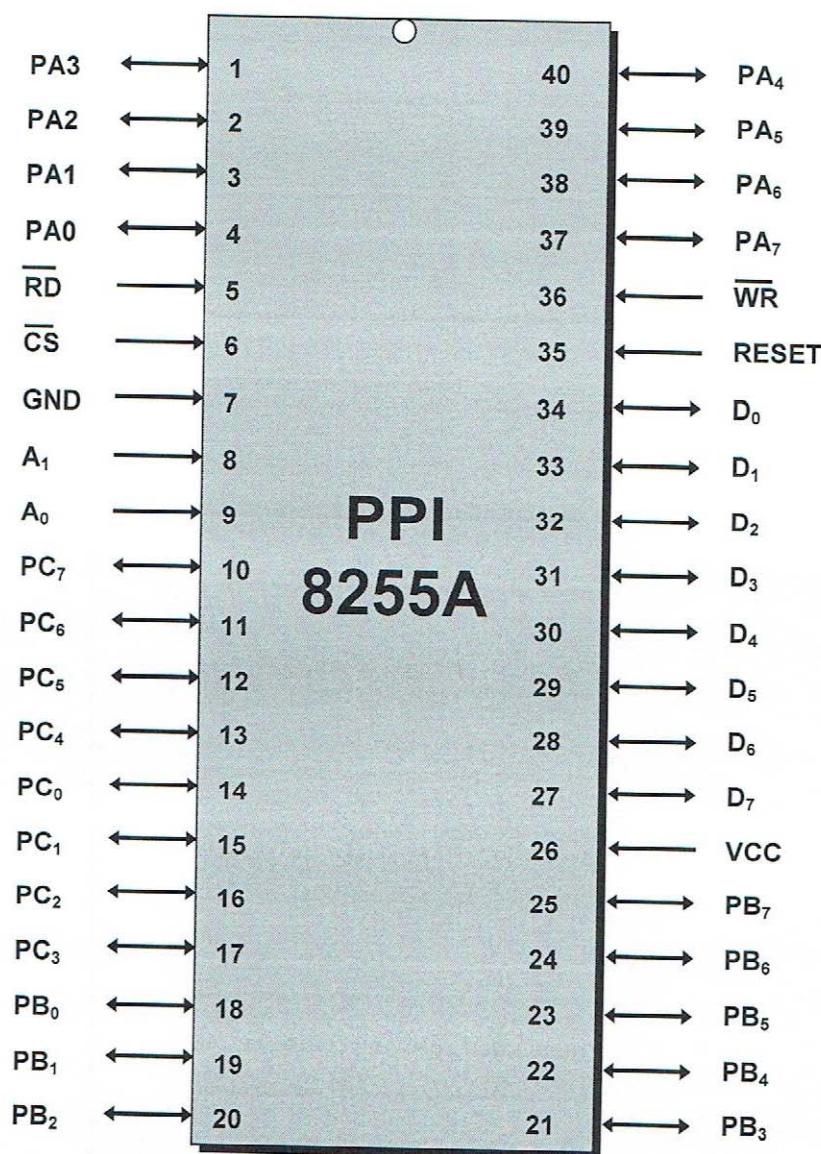

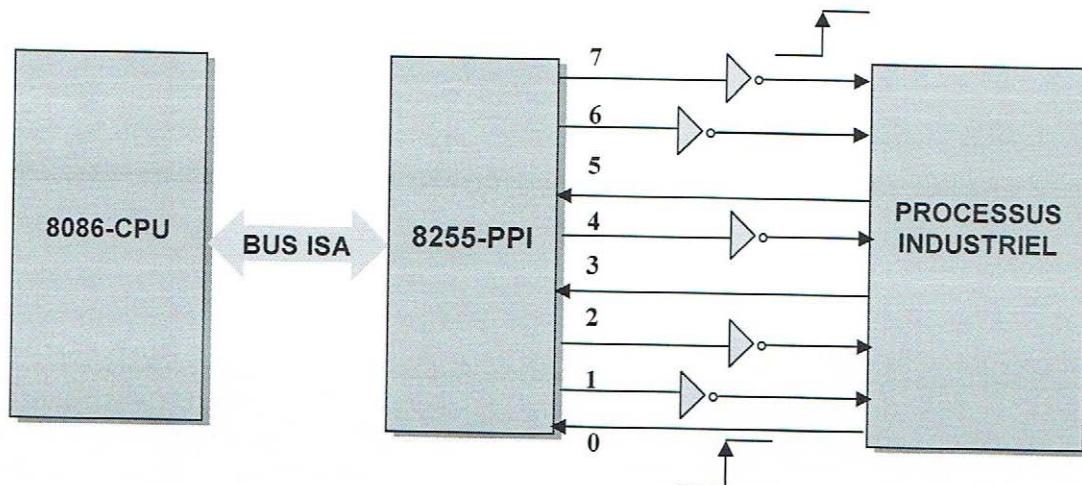

| III Description du PPI                                           | 129 |

| III.1 Liaisons avec le 8086                                      | 129 |

| III.2 Liaisons avec la périphérie                                | 130 |

| IV Description interne du PPI                                    | 130 |

| IV.1 Registres de données                                        | 130 |

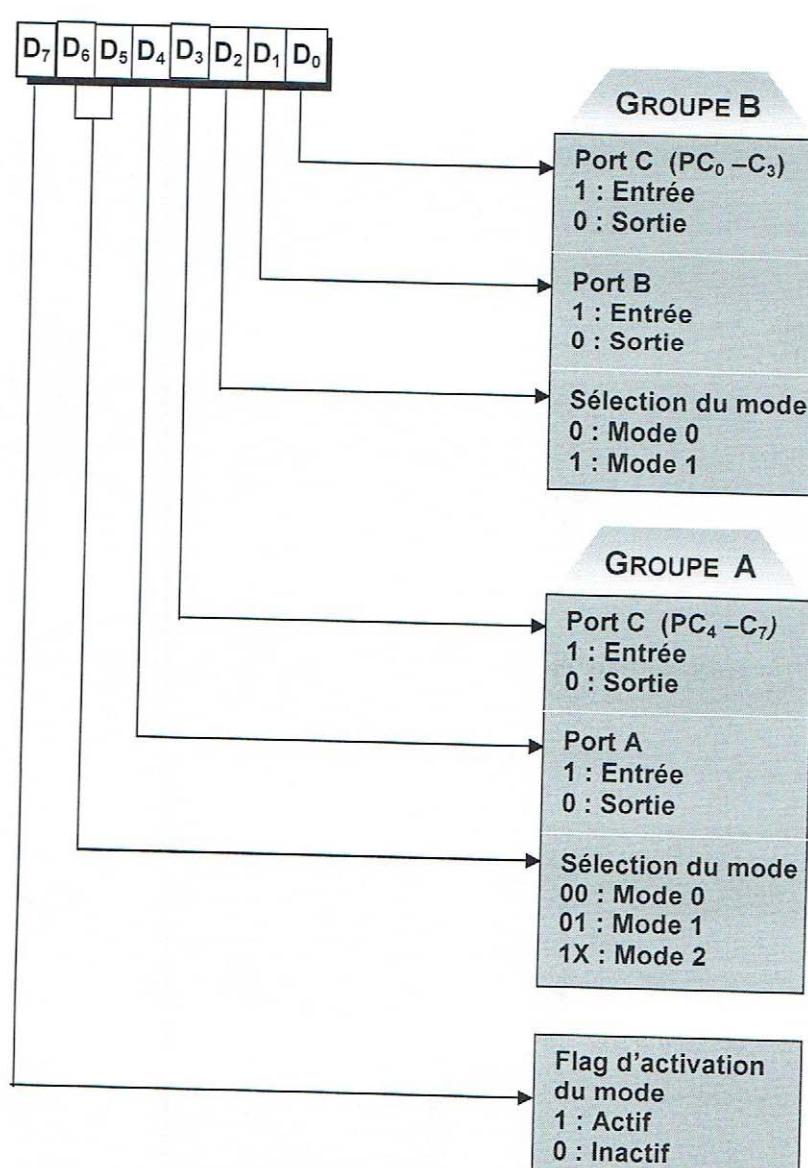

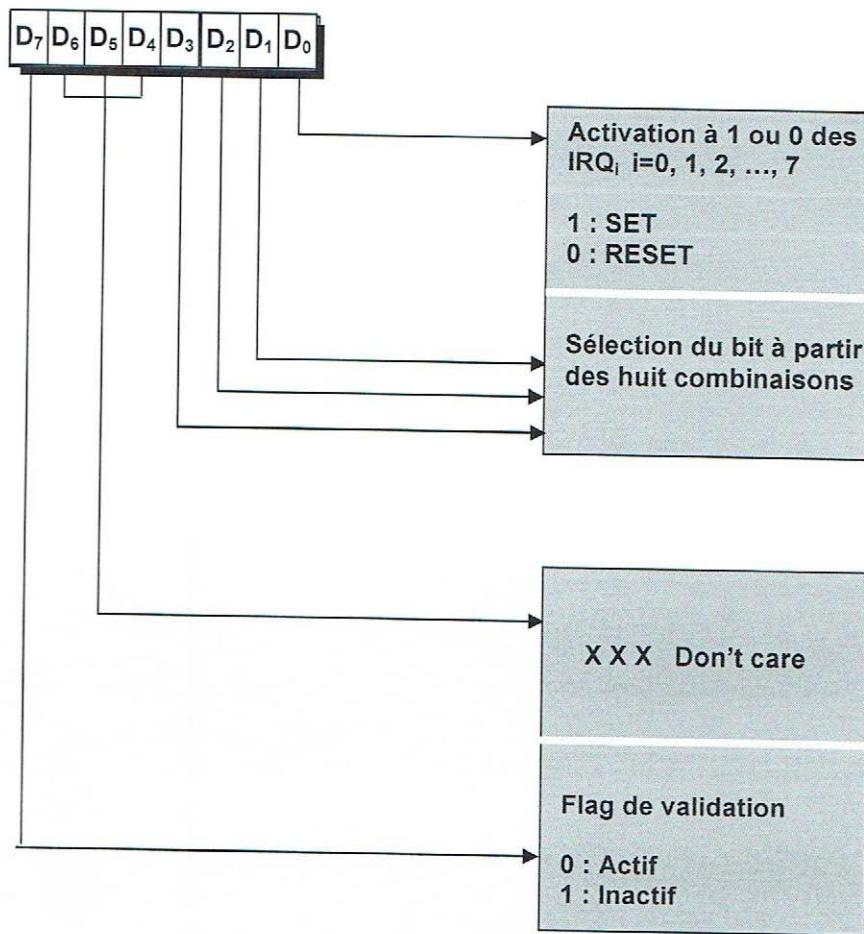

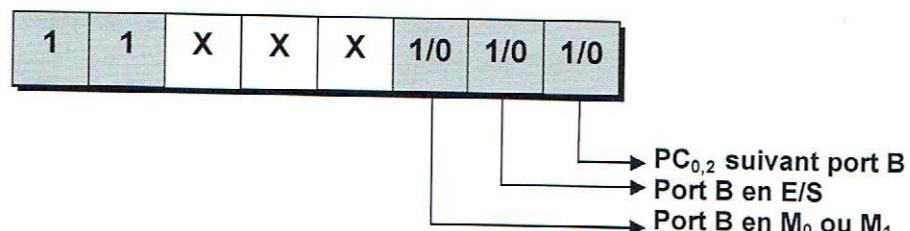

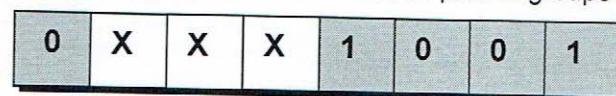

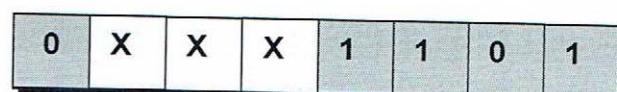

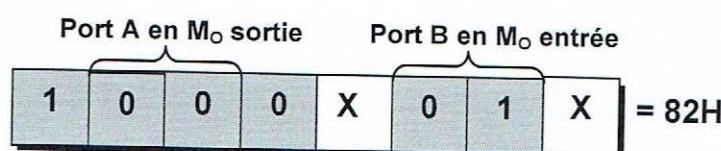

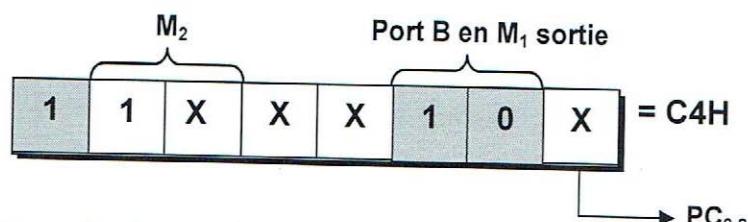

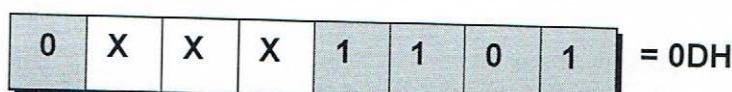

| IV.2 Registre de contrôle                                        | 133 |

| V Description opérationnelle du PPI                              | 134 |

| V.1 Mode 0: Mode d'Entrées/Sorties de base                       | 134 |

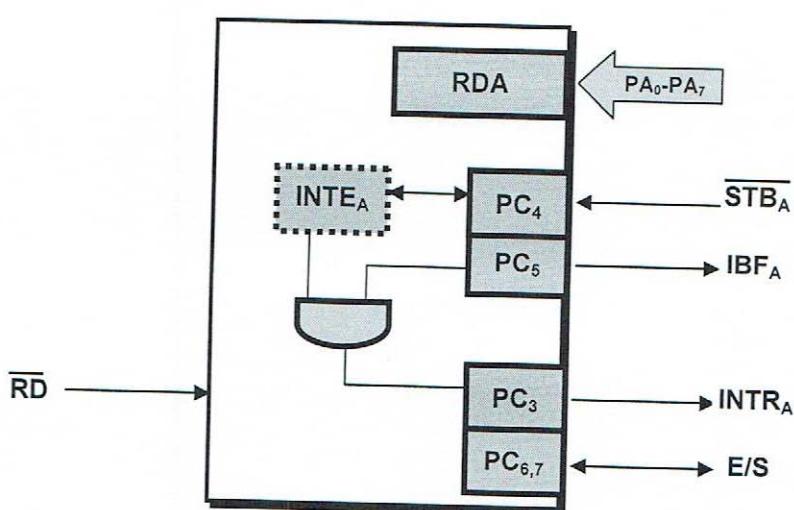

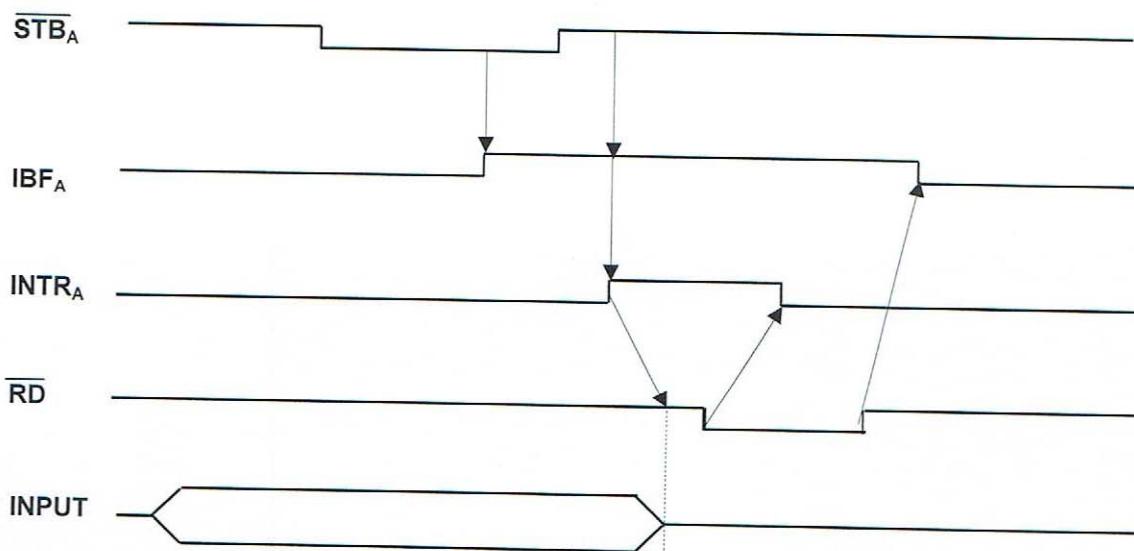

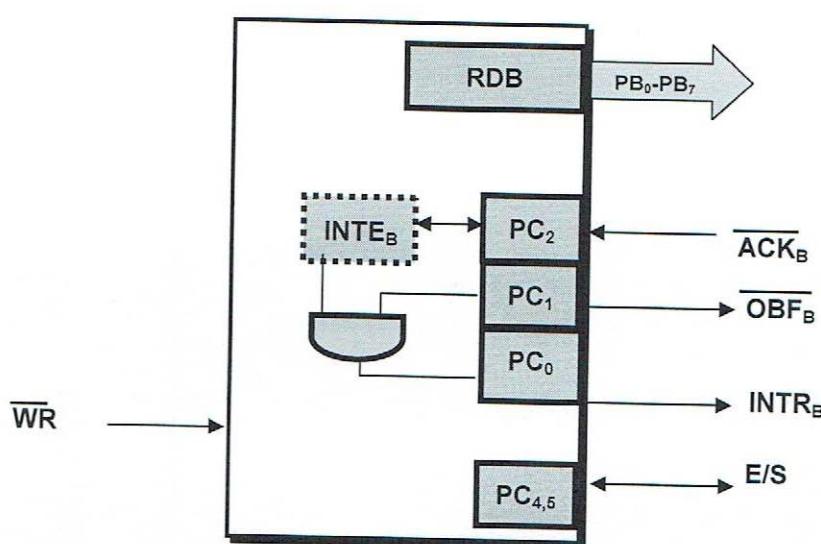

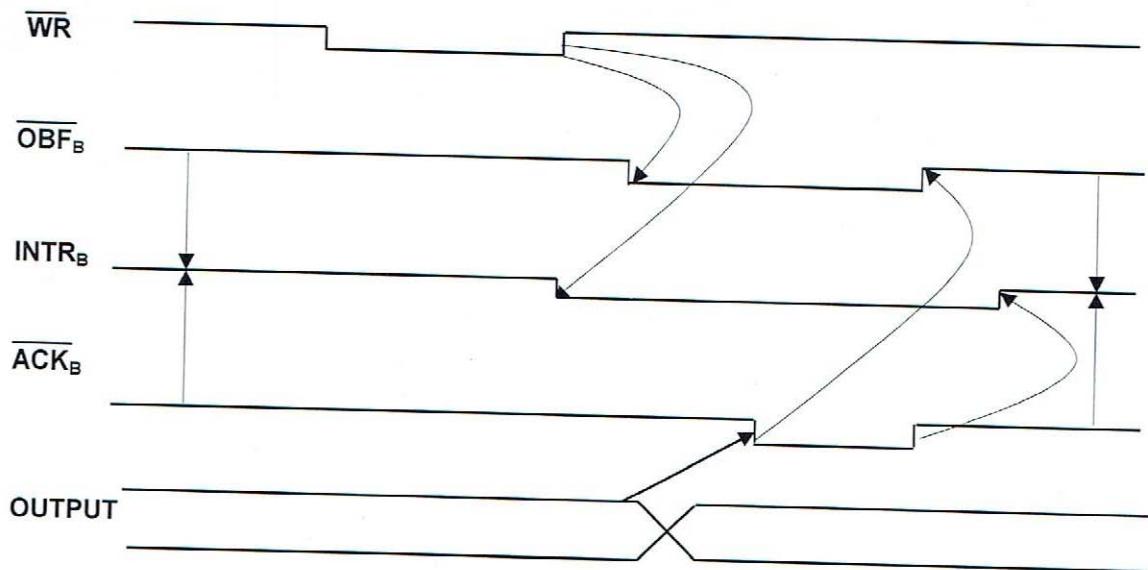

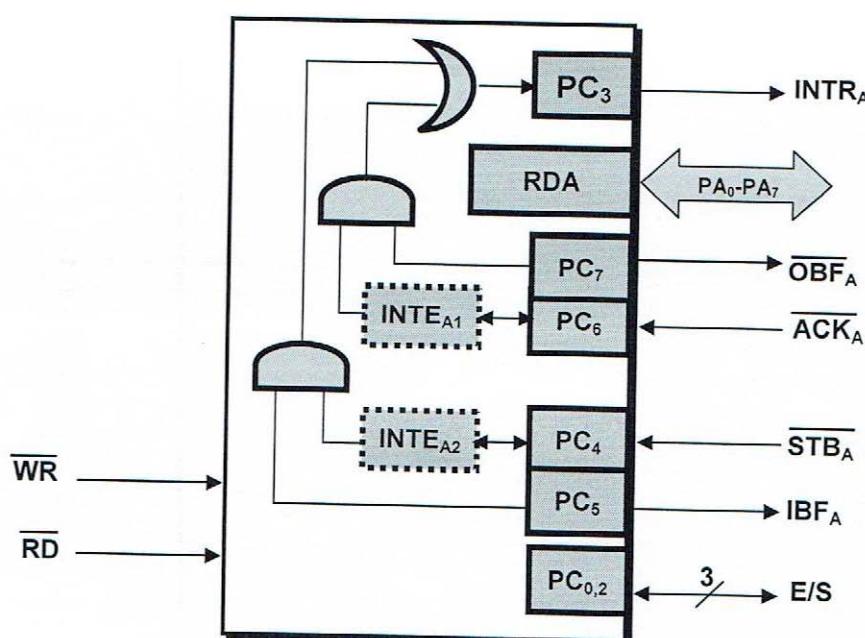

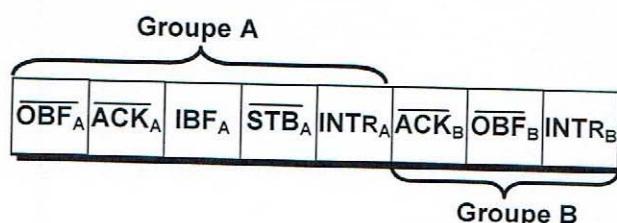

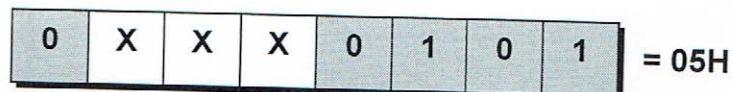

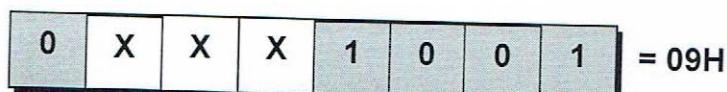

| V.2 Mode 1: Mode d'Entrées/Sorties avec signaux de dialogue      | 135 |

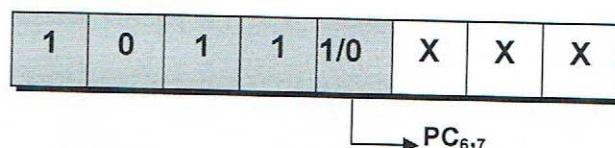

| V.3 Mode 2: Mode bidirectionnel avec signaux de dialogue         | 139 |

| VI Programmation du PPI                                          | 141 |

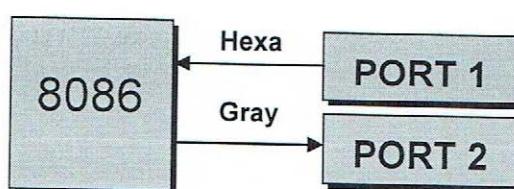

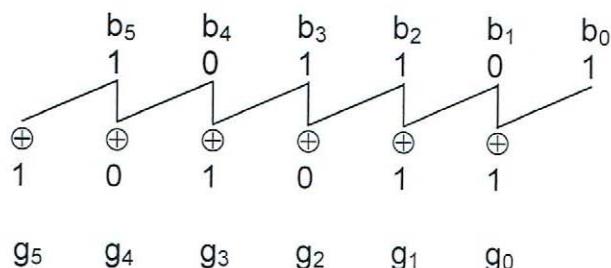

| VI.1 Exemple de programmation du PPI                             | 141 |

| <b>CHAPITRE 10</b>                                               |     |

| <b>CIRCUIT D'ENTREES ET DE SORTIES SERIEL ET PROGRAMMABLE</b>    | 144 |

| I Introduction                                                   | 144 |

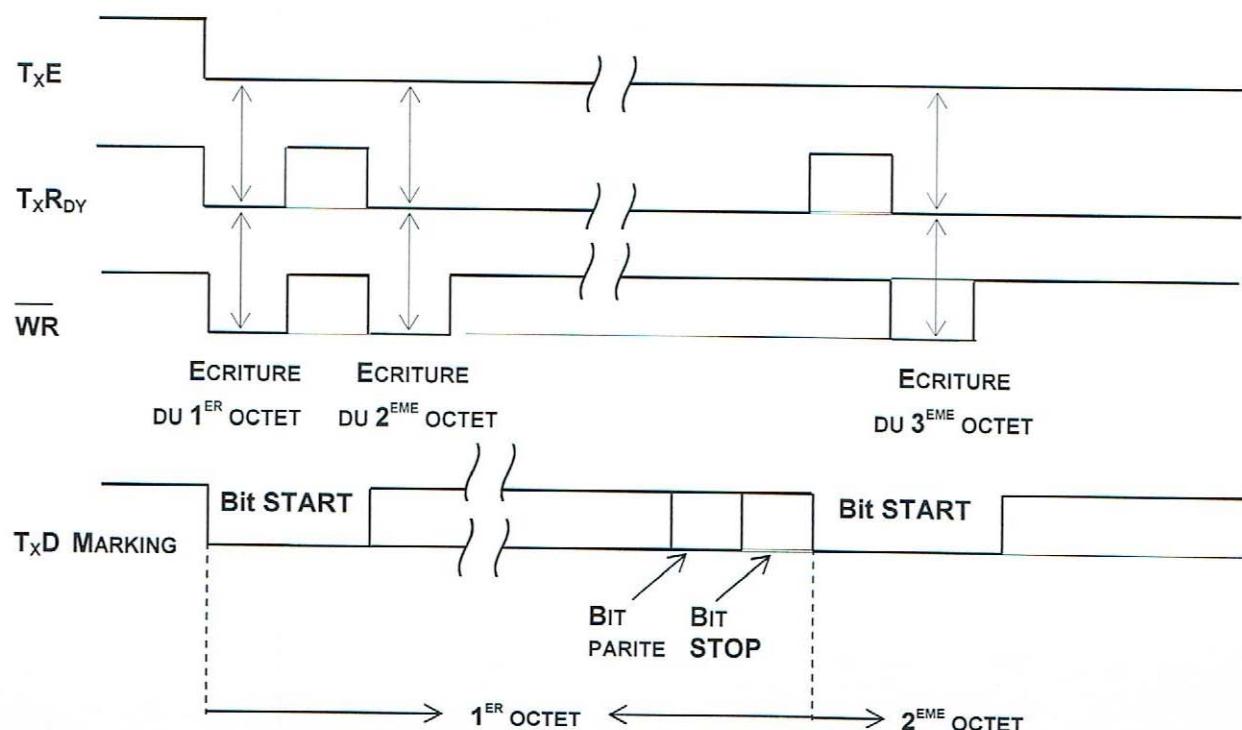

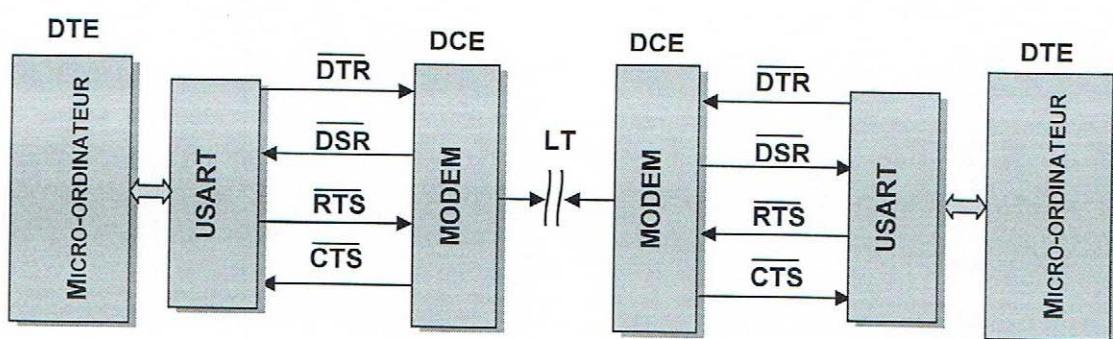

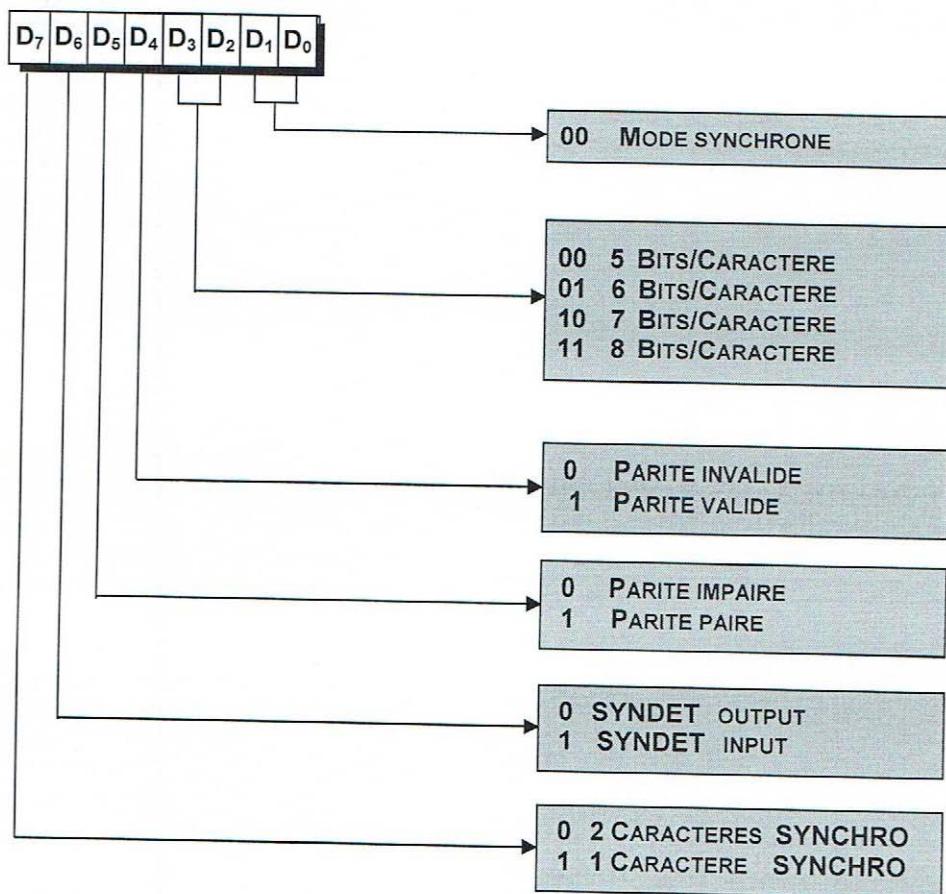

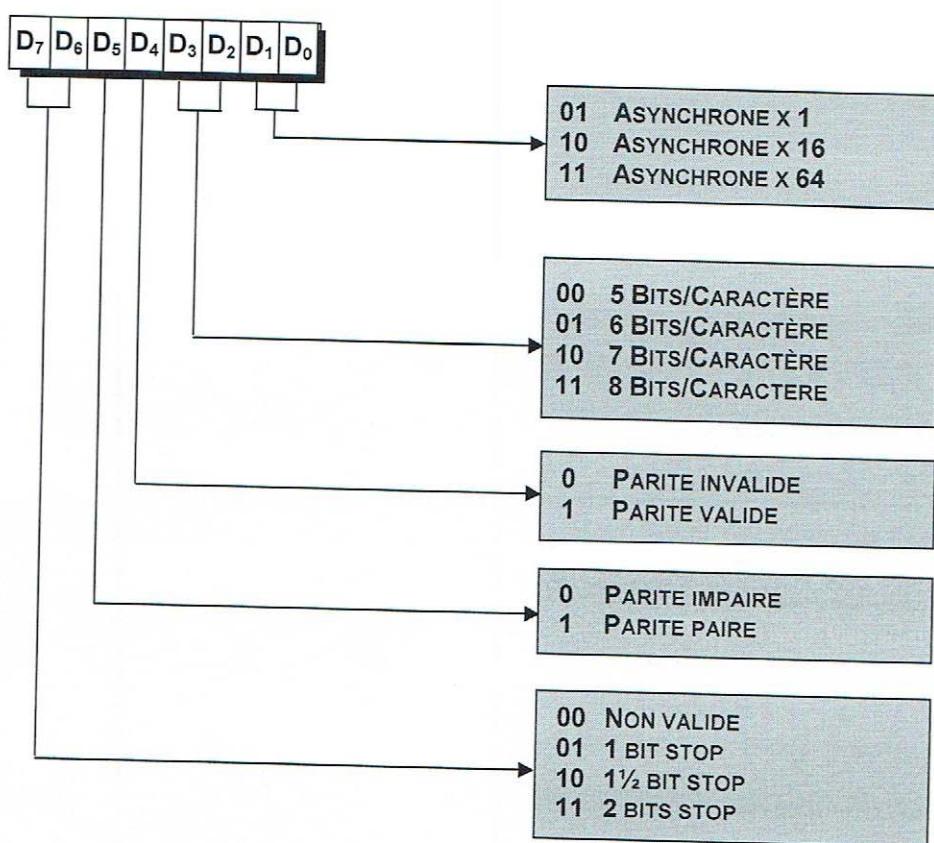

| II Principes de base de la communication serielle                | 144 |

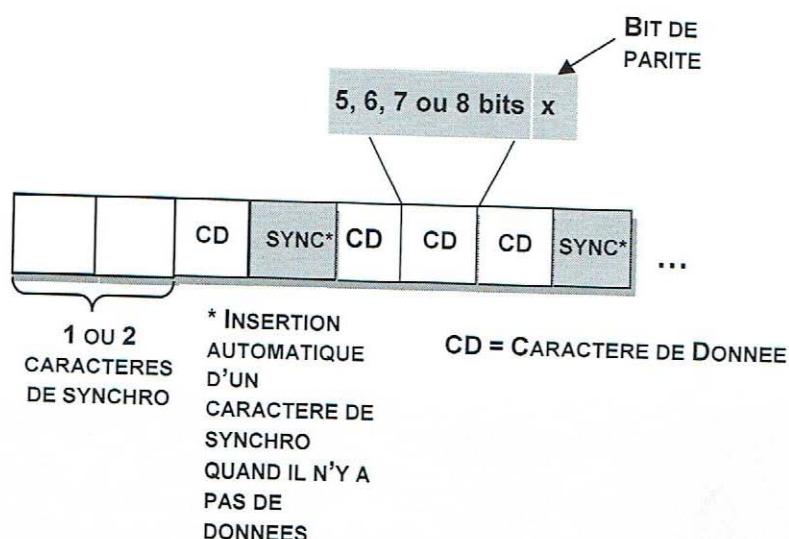

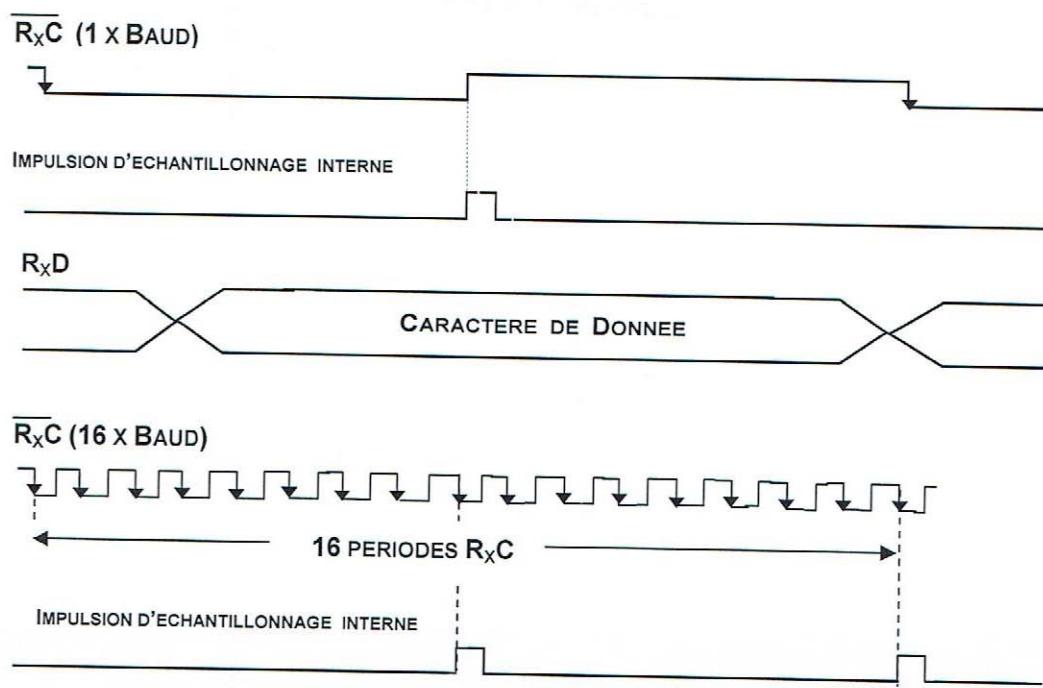

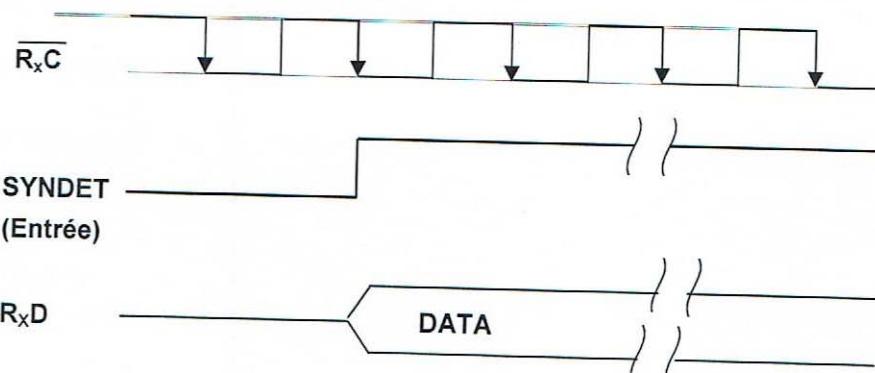

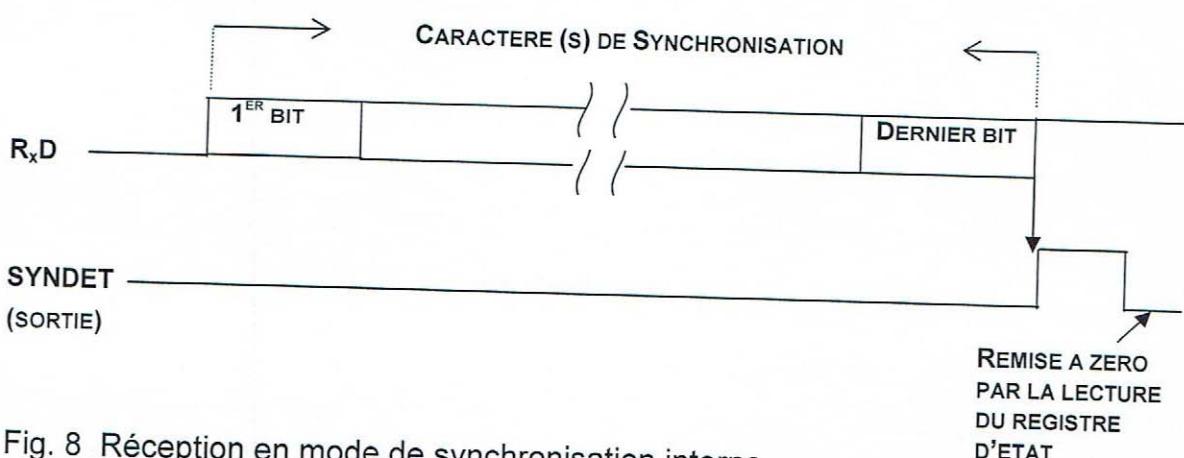

| II.1 Communication serielle synchrone                            | 144 |

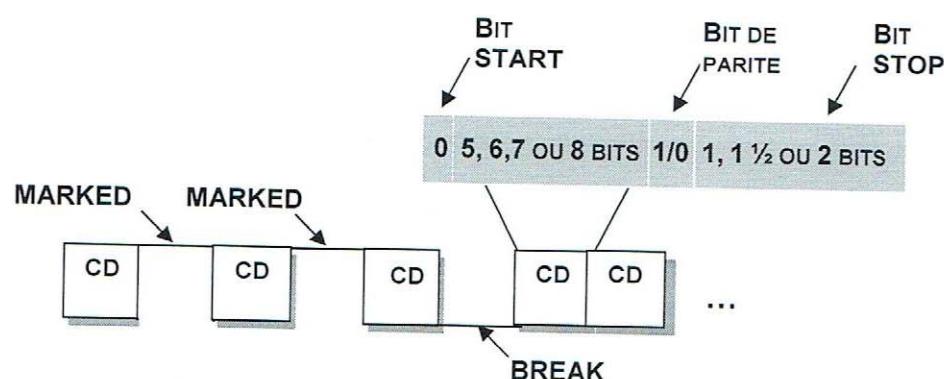

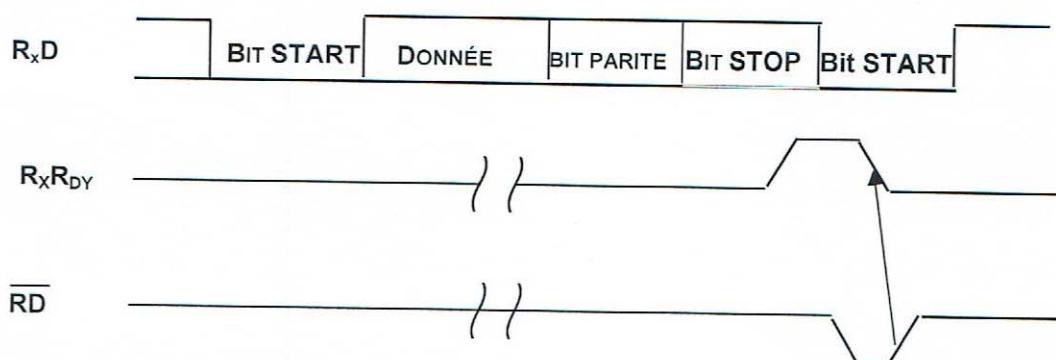

| II.2 Communication serielle asynchrone                           | 145 |

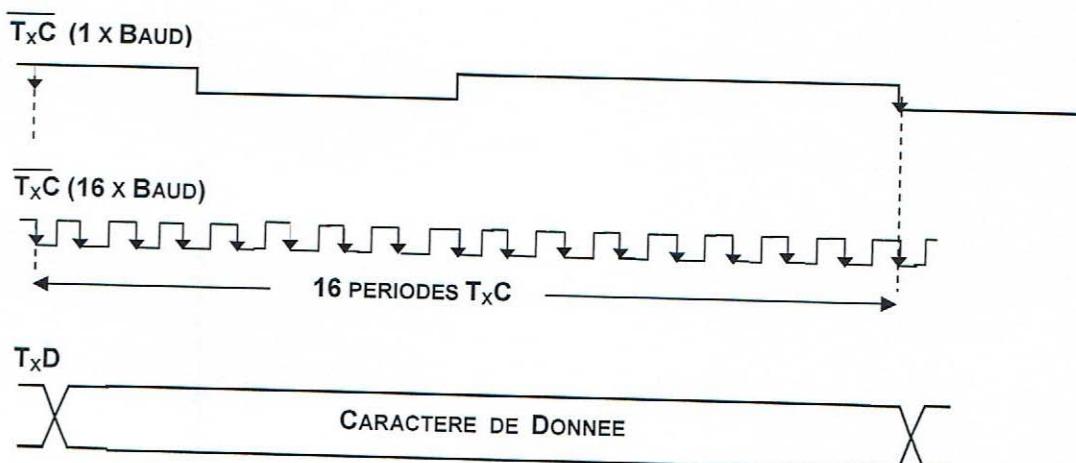

| II.3 Bit Rate et Baud Rate                                       | 146 |

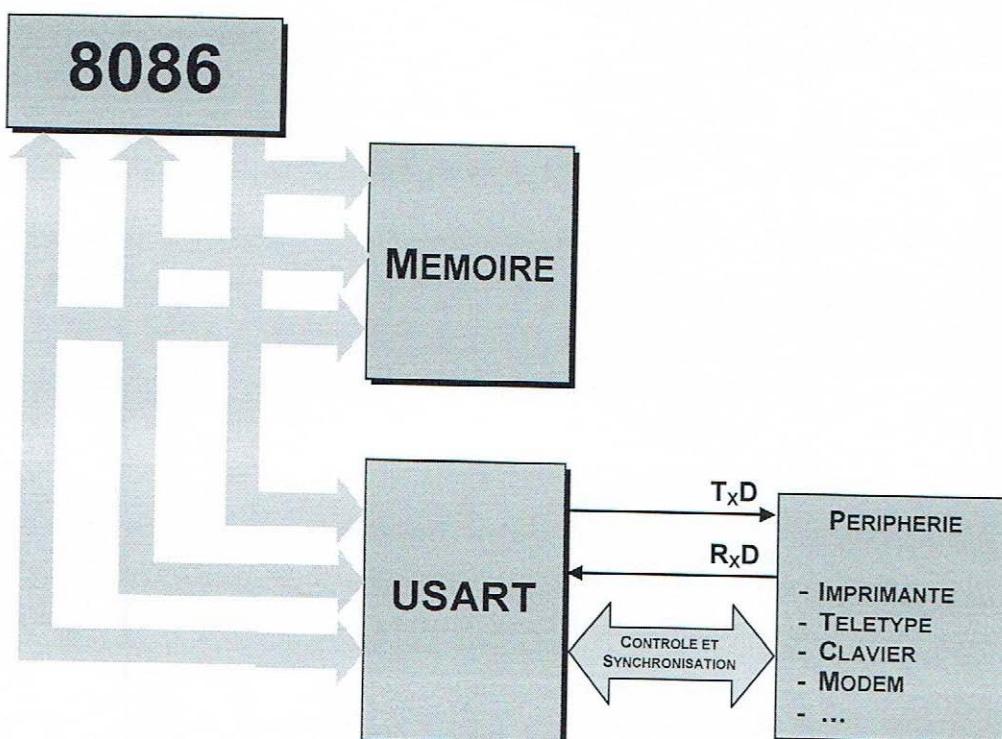

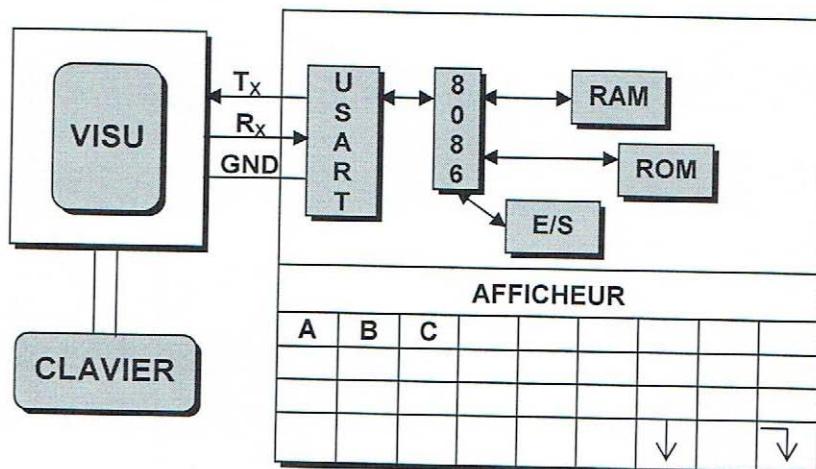

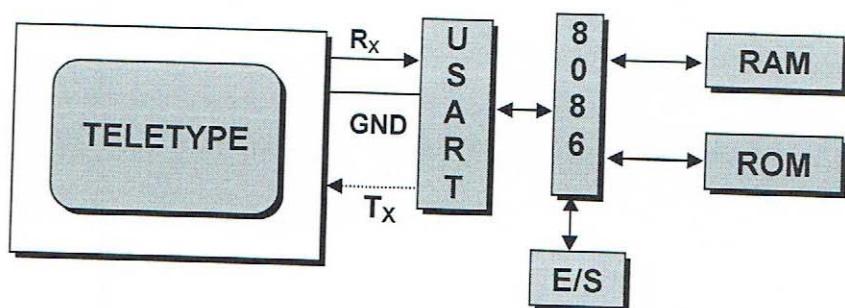

| III USART (8251)                                                 | 146 |

| III.1 Caractéristiques de l'USART                                | 147 |

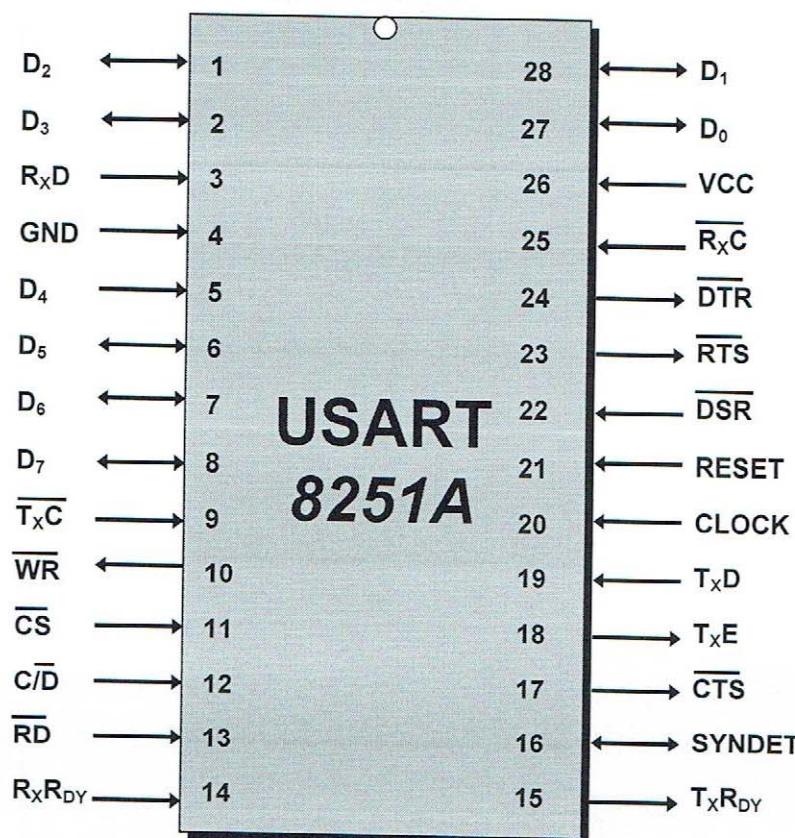

| III.2 Description externe de l'USART                             | 148 |

|                                          |     |

|------------------------------------------|-----|

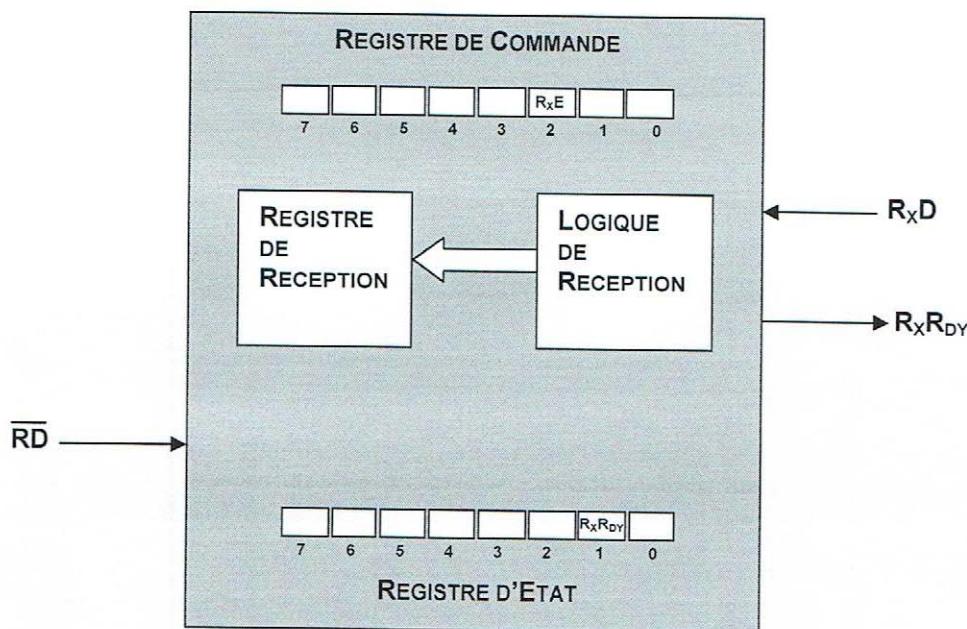

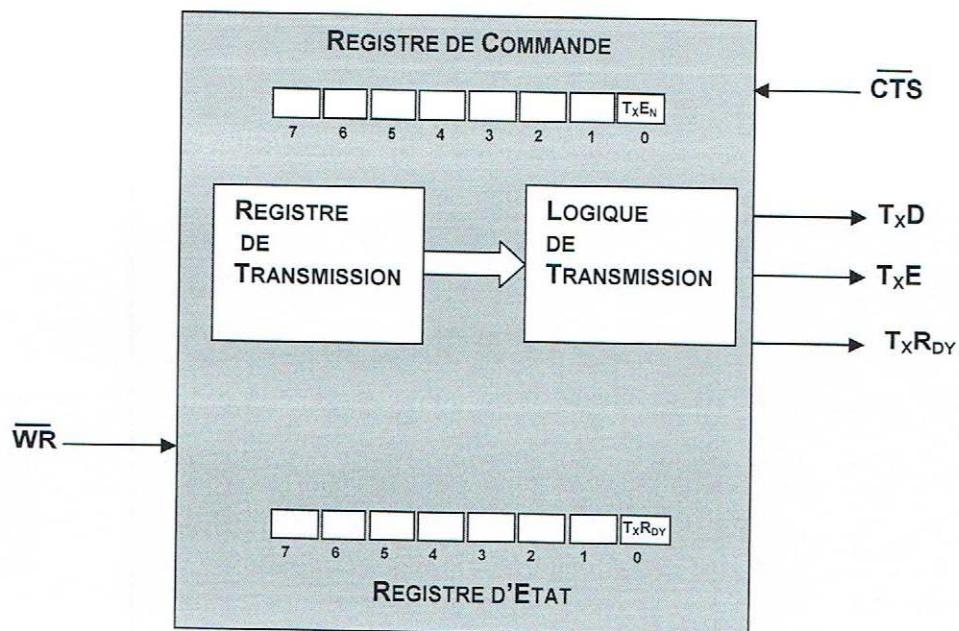

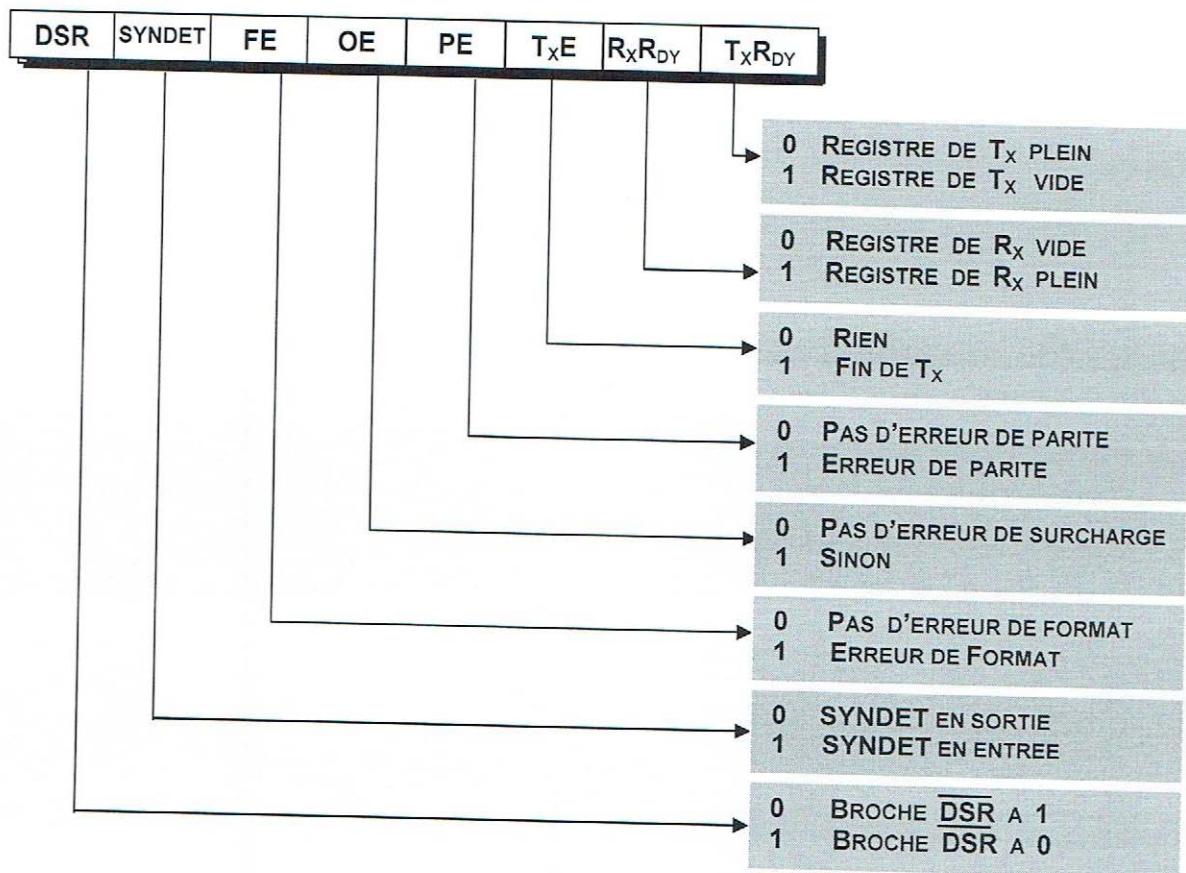

| III.3 Description interne de l'USART     | 155 |

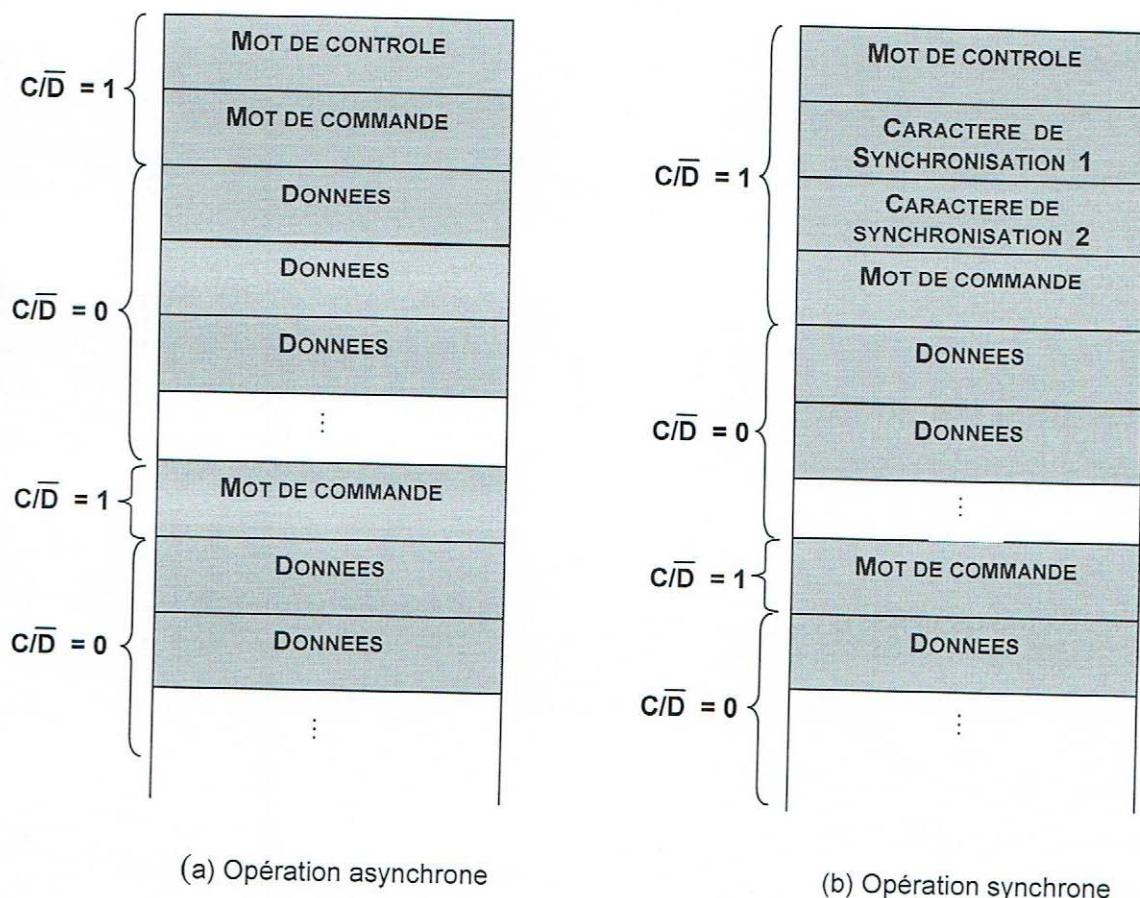

| IV Programmation de l'USART              | 160 |

| IV.1 Exemple de programmation de l'USART | 161 |

## CHAPITRE 11 INTERFACES SUR PC

|                                                         |     |

|---------------------------------------------------------|-----|

| I Introduction                                          | 163 |

| II Interface parallèle Centronics                       | 163 |

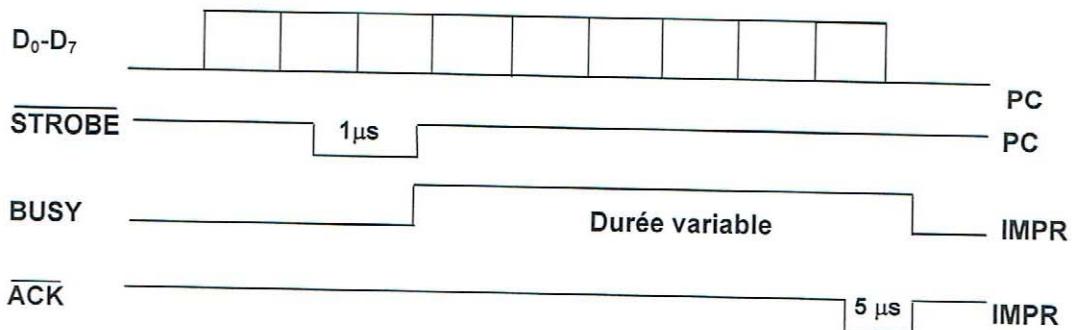

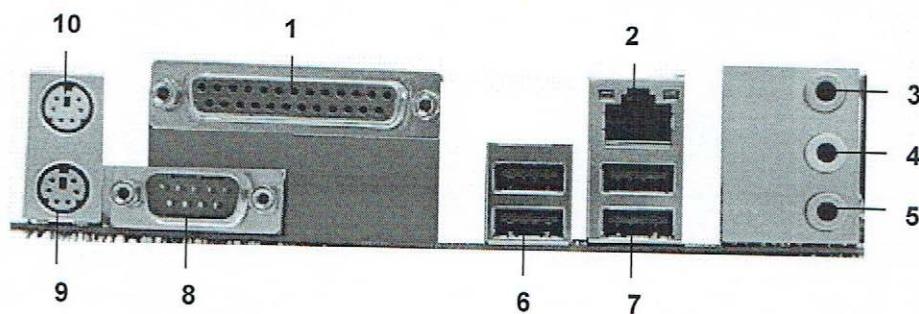

| II.1 Fonctionnement de l'interface parallèle Centronics | 164 |

| II.2 Brochage de l'interface parallèle Centronics       | 164 |

| III Interface série RS 232 (1969)                       | 165 |

| III.1 Définition de la norme RS 232                     | 165 |

| III.2 Brochage de la RS232                              | 166 |

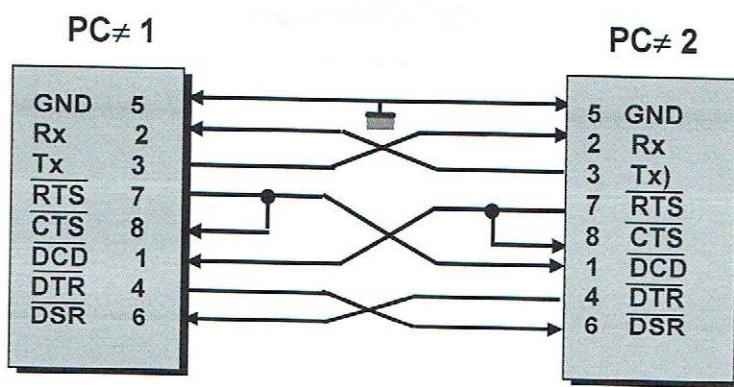

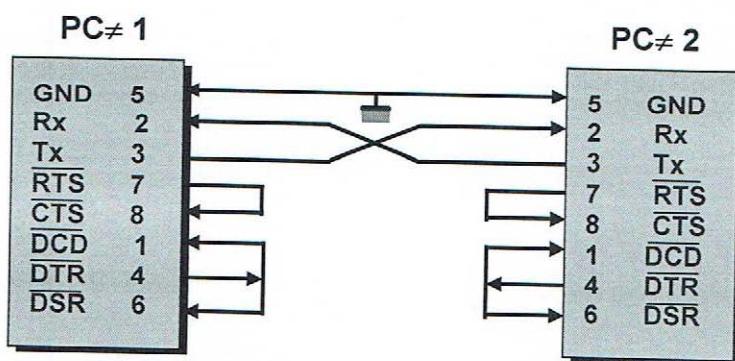

| III.3 Liaison NULL-MODEM (MOdulation-DEModulation)      | 167 |

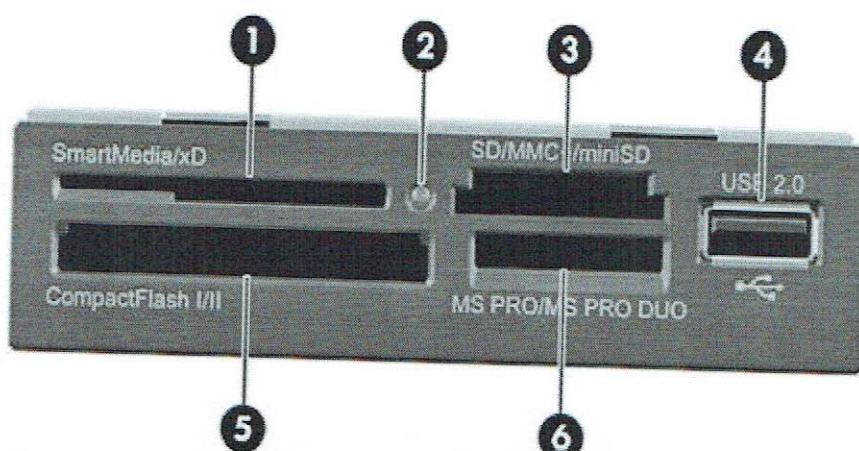

| IV Interface ou bus USB (Universal Serial Bus)          | 168 |

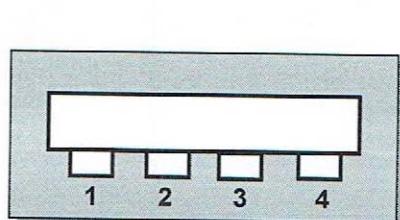

| IV.1 Types de connecteurs USB                           | 169 |

| IV.2 Fonctionnement du bus USB                          | 169 |

## EXERCICES

|                     |     |

|---------------------|-----|

| TRAVAUX DIRIGÉS N°1 | 171 |

| TRAVAUX DIRIGÉS N°2 | 175 |

| TRAVAUX DIRIGÉS N°3 | 182 |

| TRAVAUX DIRIGÉS N°4 | 185 |

| TRAVAUX DIRIGÉS N°5 | 192 |

| TRAVAUX DIRIGÉS N°6 | 212 |

| TRAVAUX DIRIGÉS N°7 | 223 |

## MANIPULATIONS

|                       |     |

|-----------------------|-----|

| TRAVAUX PRATIQUES N°1 | 237 |

| TRAVAUX PRATIQUES N°2 | 240 |

| TRAVAUX PRATIQUES N°3 | 243 |

| TRAVAUX PRATIQUES N°4 | 246 |

| TRAVAUX PRATIQUES N°5 | 249 |

| TRAVAUX PRATIQUES N°6 | 255 |

| TRAVAUX PRATIQUES N°7 | 260 |

## **ANNEXES**

|                                         |     |

|-----------------------------------------|-----|

| <b>ANNEXE 1</b>                         |     |

| CIRCUITS ANNEXES DU 8086                | 261 |

| <b>ANNEXE 2</b>                         |     |

| SYNOPTIQUES DE QUELQUES IBM PC          | 266 |

| <b>ANNEXE 3</b>                         |     |

| JEU D'INSTRUCTIONS DU 8086              | 278 |

| <b>ANNEXE 4</b>                         |     |

| COMMANDES DU SIMULATEUR DU 8086         | 290 |

| <b>ANNEXE 5</b>                         |     |

| CODE ASCII                              | 299 |

| <b>ANNEXE 6</b>                         |     |

| REPRESENTATION DES NOMBRES DANS LE 8087 | 304 |

| <b>ANNEXE 7</b>                         |     |

| INTERRUPTIONS BIOS ET DOS USUELLES      | 306 |

| <b>REFERENCES BIBLIOGRAPHIQUES</b>      | 312 |

# PRÉFACE

Lorsque Gordon Moore, co-fondateur d'Intel, avait prédit en 1965 que la densité en transistors des circuits intégrés allait doubler tous les deux ans, savait-il que sa prédition allait se confirmer avec une précision inouïe jusqu'à aujourd'hui? Nous constaterons qu'entre temps la vitesse des calculateurs a augmenté à peu près au même rythme que l'accroissement du taux d'intégration.

Bien que les machines algorithmiques ne semblent pas avoir de lien direct avoir l'architecture des PC, elles demeurent quand même une source introductrice du microprocesseur dont l'unité de commande matérialise l'algorithme d'interprétation du répertoire d'instructions. De part ce fait, les automates de commande tels l'incrémental est celui de Wilkes, que nous avons étudiés dans le chapitre 1, peuvent convenir à introduire les architectures de Von Neumann et Harvard et les technologies CISC, RISC et WISC. Il n'en demeure pas moins que l'enseignant en charge de ce cours soit libre des ses choix.

S'il nous sera reproché à juste titre que l'exposé du chapitre 2 reste incomplet non pas relativement au phénomène de mode, mais du fait des limites théoriques imposées par la structure même de l'IBM PC-XT (absence des concepts des mémoires cache, virtuelle et paginée, des RAM vidéo et shadowing, interfaces multimédia, chipsets, etc. ...), nous renvoyons à ce sujet le lecteur intéressé à la littérature spécialisée. Néanmoins, pour orienter les curieux et assouvir la faim des insatiables, nous présentons, dans le chapitre 3, un aperçu succinct de l'évolution vertigineuse de la technologie des micro-ordinateurs de la famille Intel et des différents chipset, bus, interfaces, mémoires et disques durs actuels.

En 1971, Intel surprend toute la planète en lançant le premier microprocesseur 4 bits. Il s'agissait du 4004 (2300 transistors et 60000 instructions par seconde). Depuis, on ne le répétera jamais assez, Intel n'arrête pas de créer l'événement en annonçant régulièrement de nouveaux produits toujours plus performants et en honorant ses annonces.

Pour une technologie en perpétuel mouvement nous ne pouvons nous donner la prétention de rendre fait de l'état de l'art et notre exposé se veut avant tout didactique. Notre choix s'est donc délibérément porté sur le microprocesseur 8086 de Intel, chapitres 4-6. En effet celui-ci, au même titre que les machines IBM PC-XT qui en sont équipées, réunit dans une large mesure toute la théorie moderne des machines universelles telle qu'elle a été édictée par Johannes Von

Neumann (1945). Par ailleurs, de part sa compatibilité ascendante, il constituera un outil d'apprentissage idéal où l'application pratique peut se réaliser sur n'importe quelle machine de fabrication ultérieure dans un parc très largement doté.

Sans montrer beaucoup de détails, le chapitre 7 reprend succinctement les modes de transferts des entrées en sorties dans les systèmes à microprocesseurs. Au vu de l'évolution vertigineuse du taux d'intégration dans les microprocesseurs, l'accent a été mis sur le mode des entrées et sorties par les interruptions.

Pour ce faire, nous savons, chapitre 8, que c'est précisément, en présence d'un nombre important de périphériques que les interruptions étaient toute leur efficacité en libérant le microprocesseur de la fastidieuse tâche de scrutation, améliorant du coup, d'une façon significative, les performances du système. Le PC est un exemple typique dans lequel les périphériques de base sont exclusivement pris en charge concomitamment par les interruptions BIOS et MS-DOS et les interruptions matérielles (Clavier, horloge cyclique, interface parallèle, interface série, contrôleur disque dur, contrôleur de lecteur disquettes et RTC/RAM CMOS dans les PC AT).

Ce qui apporte le plus de complication dans la conception d'un système, en logique programmée c'est la communication microprocesseur-périphérie. La raison tient essentiellement au fait qu'il n'y ait aucune standardisation dans les périphériques de sorte qu'un microprocesseur ne peut pas, en général, commander directement les périphériques. Un circuit intégré d'adaptation appelé interface s'avère nécessaire entre le microprocesseur et les périphériques. A de très rares exceptions près. L'interface établit donc une compatibilité entre les entrées et sorties du microprocesseur et celles des périphériques, tant au niveau du type de transmission (série ou parallèle), qu'au niveau du code (ASCII, EBCDIC, ISO, ...) ou alors au niveau de la vitesse de transmission. Pour ce faire, les chapitres 9-10 étudient, respectivement, un exemple d'interface parallèle et celui d'un interface série.

Enfin, le chapitre 11 introduit les deux types d'interfaces de communication qui existent sur les PC, à savoir, les interfaces parallèle (Centronix) et série (RS232 et USB). Remarquons, cependant que cette dernière décennie a connu une montée en puissance de l'interface série USB. A l'heure actuelle, tous les PC en sont dotés en nombre important, provoquant ainsi la disparition de l'interface parallèle.

A l'exception des chapitres 7 et 11, tous les autres sont ponctués chacun par une série d'exercices et de manipulations sur micro-ordinateur, organisées

respectivement, sous forme de travaux dirigés et de travaux pratiques. Ces derniers ont été élaborés à l'issu de plusieurs années d'enseignement des systèmes à microprocesseurs.

Enfin, à la fin du manuscrit, les annexes constituent un support pour la compréhension de certaines sections abordées aux différents chapitres, travaux dirigés et travaux pratiques.

# CHAPITRE 1

## MACHINES ALGORITHMIQUES

### I Introduction

Tout processus de traitement d'information numérique est considéré comme un calcul au sens algébrique du terme. L'exécution d'un calcul repose sur la mise en œuvre d'un algorithme, défini de la manière suivante:

- 1- Un algorithme est l'assemblage de primitives de calcul selon un ensemble de règles de construction admissibles.

- 2- Pour un concepteur de processeur, la matérialisation de la primitive de calcul devient l'idée centrale autour de laquelle sera élaboré l'ensemble du schéma architectural.

### II Notion d'automate fini

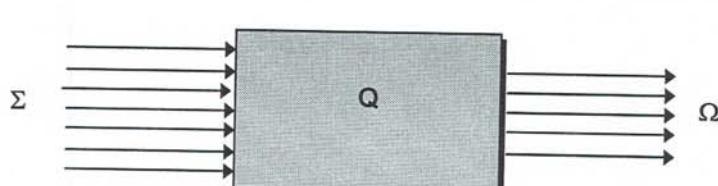

Un automate fini peut se définir comme un système algébrique  $A = < \Sigma, \Omega, Q, M, N >$ , où

$\Sigma$  : Ensemble fini des variables d'entrée.

$\Omega$  : Ensemble fini des variables de sortie.

$Q$  : Ensemble fini des variables d'état interne.

$M : \Sigma \times Q \rightarrow Q$  Fonction de transition, associe l'état actuel à l'état suivant.

$N : Q \rightarrow \Omega$  Fonction de sortie, associe l'état interne à la sortie.

Fig. 1 Schématisation d'un automate fini

Un automate ainsi défini s'appelle automate de MOORE. Il existe un second type d'automate appelé, automate de MEALY, qui se différencie du premier par le fait que la fonction de sortie dépend non seulement de l'état interne, mais aussi des variables d'entrée tel que  $N : \Sigma \times Q \rightarrow \Omega$ .

### III Matérialisation de la primitive de calcul par un circuit logique combinatoire

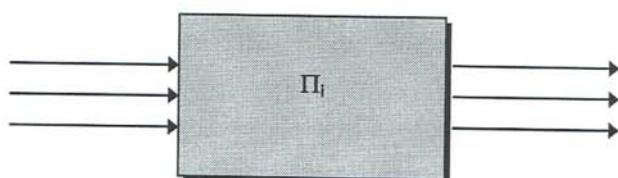

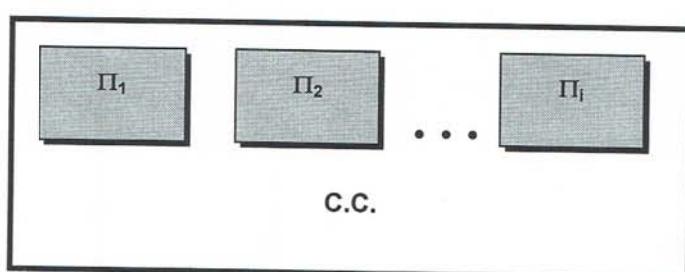

Les opérateurs réalisant les primitives de calcul peuvent être des circuits logiques, des réseaux logiques programmables (PLA), ou des mémoires mortes (ROM). Ils seront appelés indifféremment ressources. On les symbolisera par une boîte noire notée  $\Pi_i$ .

Fig. 2 Schématisation d'une ressource

Le circuit logique combinatoire consiste en une interconnexion sans boucle des ressources. Il sera noté C. C.

Fig. 3 Schéma synoptique d'un circuit combinatoire

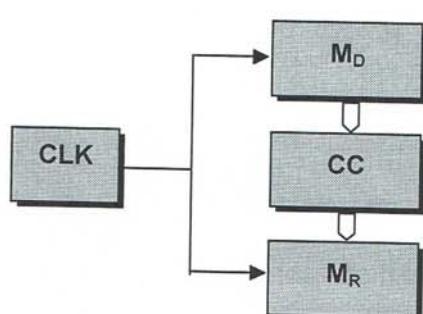

En introduisant un registre mémoire de donnée  $M_D$  et un registre mémoire résultat  $M_R$ , la primitive de calcul sera représentée par un transfert fonctionnel  $[M_R] := f ([M_D])$ , où  $f$  est une fonction arithmétique ou logique. On aboutit à l'organisation schématisée de la Figure 4.

Fig. 4 Schématisation d'un transfert fonctionnel

Cette réalisation comporte, outre les mémoires  $M_R$ ,  $M_D$  et la ressource CC, l'embryon d'un circuit de commande CLK, représenté par exemple par l'impulsion électrique qui décide du moment où s'effectue le transfert.

Une telle réalisation est appelée circuit combinatoire parce que la valeur mémorisée en  $M_R$  lors d'un cycle d'évolution ne dépend que du contenu de  $M_D$  lors de ce cycle et non de l'histoire antérieure du circuit. Nous l'appellerons système à temps d'exécution unité.

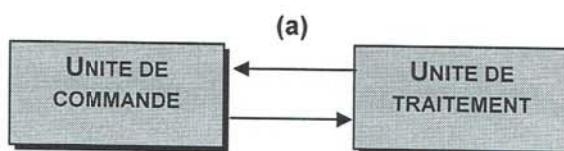

#### IV Modèle de Glushkov

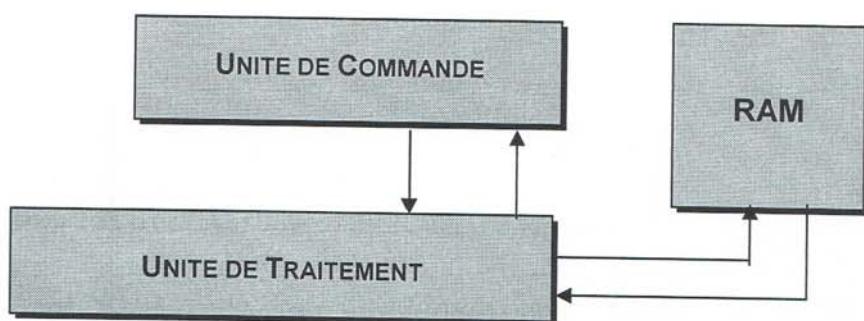

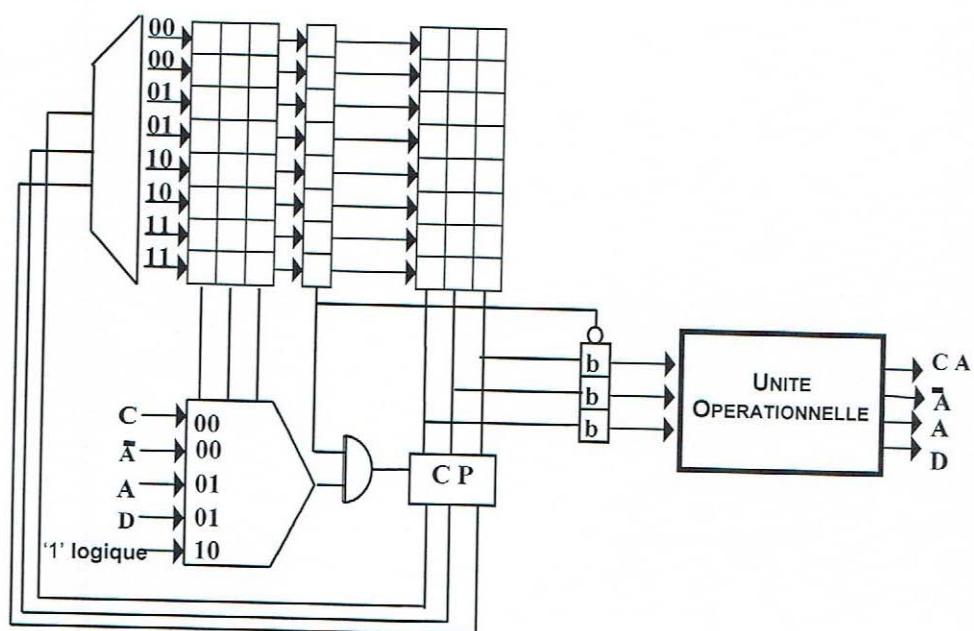

Dans ce qui précède, nous avons vu la décomposition naturelle d'un système de calcul en deux sous-ensembles autonomes: l'unité de commande et l'unité de traitement. Dans le modèle de Glushkov, l'unité de commande reçoit un retour d'information par le biais de la réaction (a).

Fig. 5 Schéma synoptique du modèle de Glushkov

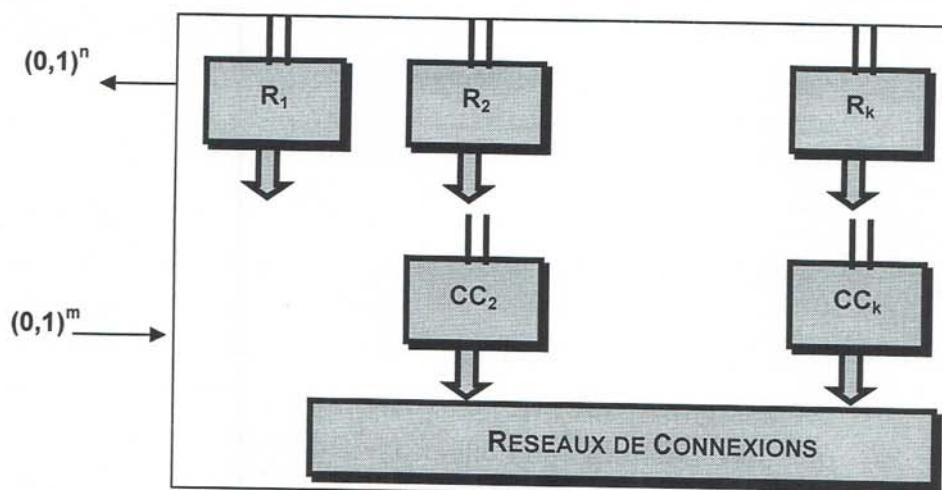

##### IV.1 Unité de traitement

Dans le cas le plus général, l'unité de traitement d'un processeur de calcul possède une structure assez régulière. Elle est constituée d'un ensemble  $\{R\}$  de registres permettant la mémorisation des grandeurs traitées, un ensemble  $\{CC\}$  de ressources matérialisant les primitives de calcul, et un réseau de connexion contrôlé permettant de mettre en rapport les registres et les ressources.

Fig. 6 Unité de traitement du modèle de Glushkov

Dans le modèle de Glushkov, l'unité de traitement répond à la définition d'un automate fini. Pour cette raison on l'appellera automate opérationnel, noté  $\langle \Sigma, \Omega, Q, M, N \rangle$ .

Les éléments de l'alphabet d'entrée  $\Sigma$  sont appelés **COMMANDES**. Chacune des commandes est représentée par un vecteur à  $m$  composantes binaires matérialisées par:

Les lignes d'activation (Enable) ou d'inhibition (Inhibit) des registres.

Les lignes de programmation des ressources.

Les lignes de contrôle du réseau de connexions.

Les éléments de l'alphabet de sortie  $\Omega$  sont codés au moyen de  $n$  variables binaires qui seront appelées variables de condition (**Status Variables, Flags**). Elles renseignent l'unité de commande sur les résultats partiels obtenus au cours de l'exécution d'un calcul.

La fonction de sortie est une application  $N: Q \rightarrow \Omega$  car les variables de condition de l'automate opérationnel ne dépendent que de l'état interne et non de la commande. L'automate opérationnel est donc un automate de Moore.

Il reste à définir la fonction de transition  $M$  de l'automate opérationnel. La taille de l'alphabet d'entrée  $\Sigma$  et de l'ensemble des états internes  $Q$  exclut la description de cette fonction par une table des phases ou un graphe d'états. Nous représenterons la fonction de transition par un langage de transfert, défini comme suit:

A chaque commande  $\sigma \in \Sigma$  s'associe une transformation  $Q \rightarrow Q$  de l'ensemble des états internes de l'automate opérationnel. Cette transformation sera décrite par l'ensemble d'équations:

$$\sigma \rightarrow L [R_i] := f_i ([R_1], [R_2], \dots, [R_k]) \quad i=1,k$$

Comme la notation  $[R]$  représente le contenu du registre  $R$ , les  $[R_i]$  au membre de droite sont relatifs au contenu précédent l'application de la commande  $\sigma$ , ceux de gauche sont les nouveaux contenus qui s'inscrivent dans les registres après l'application de cette commande.

## IV.2 Unité de commande

L'unité de commande apparaissant dans le modèle de Glushkov est, au même titre que l'unité de traitement, un automate fini. Ceci permettra de la synthétiser matériellement par des circuits combinatoires ou des circuits séquentiels synchrones.

A la lumière de la description de l'automate opérationnel, il devient évident que l'automate de commande va essentiellement compléter la matérialisation de l'algorithme de calcul à mettre en œuvre, compte tenu du langage de transfert de l'automate opérationnel.

Mishenko décrit les algorithmes de calcul par un programme, qui est constitué, par une suite d'instructions. Si les instructions représentent les fonctions de transition de l'automate de commande, nous pouvons sans ambiguïté associer programme et automate de commande.

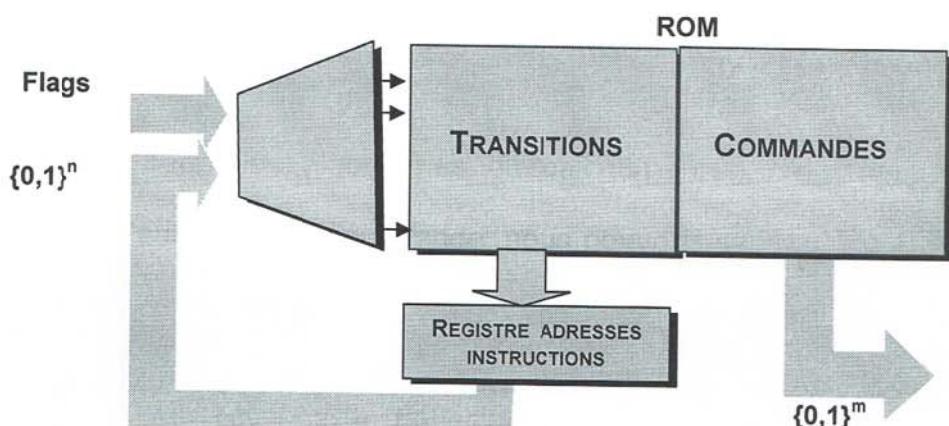

La structure la plus simple a été proposée par WILKES en 1951, Figure 7. Le programme réside dans une mémoire morte, dans laquelle s'établit une relation biunivoque entre les fonctions de transition de l'automate de commande et ses variables de sortie (Commandes). L'automate de Wilkes représente surtout un intérêt historique.

Fig. 7 Automate de WILKES

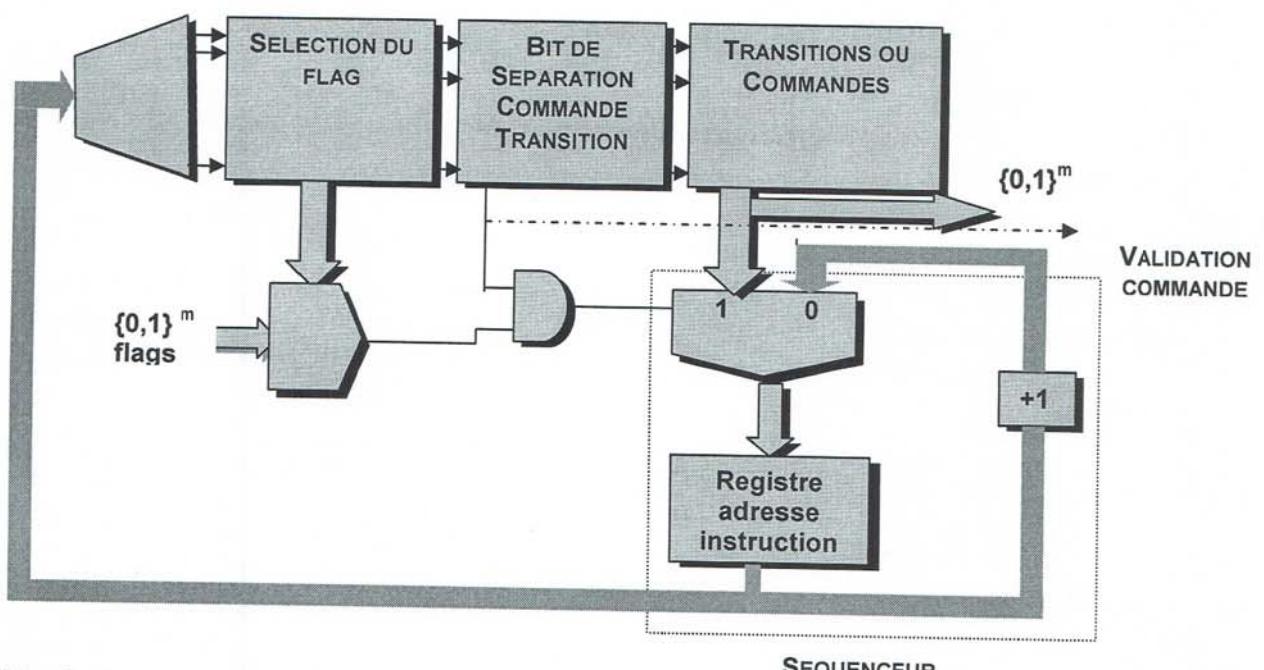

D'autres automates de commande ont été développés tel que l'automate incrémental, qui est nettement moins coûteux en espace mémoire et plus simple à programmer, moyennant une légère modification du circuit, Figure 8.

Fig. 8 Automate incrémental.

L'entrée de l'automate de commande, représentée par les variables de condition, contribue amplement à la détermination de la fonction de sortie. L'automate de commande est un automate de Mealy.

## V Microprocesseur

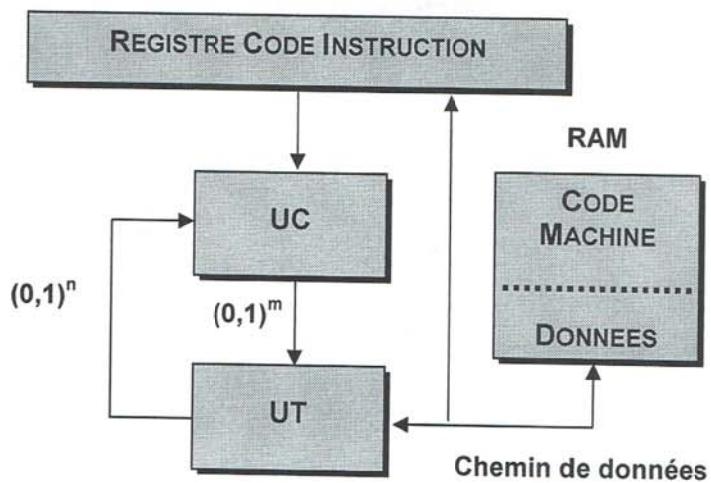

Le nombre de registres contenus dans l'unité de traitement peut s'avérer insuffisant, ou du moins technologiquement limité, pour certaines applications. Ceci nécessite un apport extérieur de mémoire vive (RAM), appelé dans un premier temps à absorber le surplus de données utilisées par l'unité de traitement. On aboutit de la sorte à une structure à trois sous-ensembles, donnée à la Figure 9.

Fig. 9 Blocs fonctionnels d'un microprocesseur

Une idée assez simple, attribuée à Johannes VON NEUMANN (1945), est la suivante:

Disposant d'une mémoire volatile destinée à l'origine à contenir des données, il serait avantageux de pouvoir y implanter des algorithmes, accordant de par ce fait un caractère d'adaptabilité et surtout d'universalité au processeur de calcul. C'est le concept de machine à programme mémorisé ou interne (Stored Program Device). Ceci à l'inverse des premiers ordinateurs dans lesquels le programme était extérieur à la machine et lui était présenté sur un ruban codé.

Le prix à payer est la conception du format optimal sous lequel seront mémorisées les instructions du programme-mémoire, et de prendre en charge leur impact sur les unités de commande et de traitement. Il faudrait aussi établir tout un système d'aiguillage des connexions, appelé chemin de données (Data Path), afin de gérer la communication entre les trois sous-ensembles.

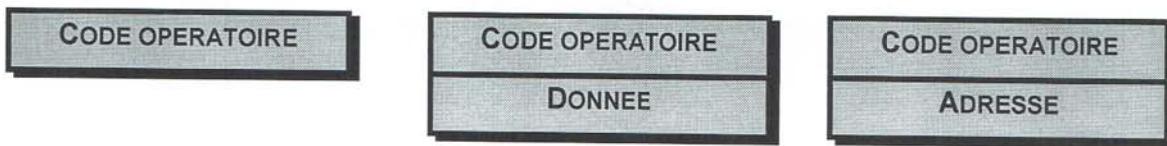

Si la contrainte d'optimalité est d'allier une relative rapidité du calcul à une occupation minimale de la mémoire volatile, nous pouvons disposer d'un alphabet assez complet en adoptant un langage qu'on appellera code machine, dans lequel toute instruction du programme-mémoire sera mémorisée sous l'un des trois formats de la Figure 10.

Fig. 10 Formats d'une instruction dans un microprocesseur

L'exécution d'un calcul dans un tel système consiste à établir une correspondance entre les instructions en code machine apparaissant dans la mémoire, et le déroulement des opérations au niveau de l'unité de traitement.

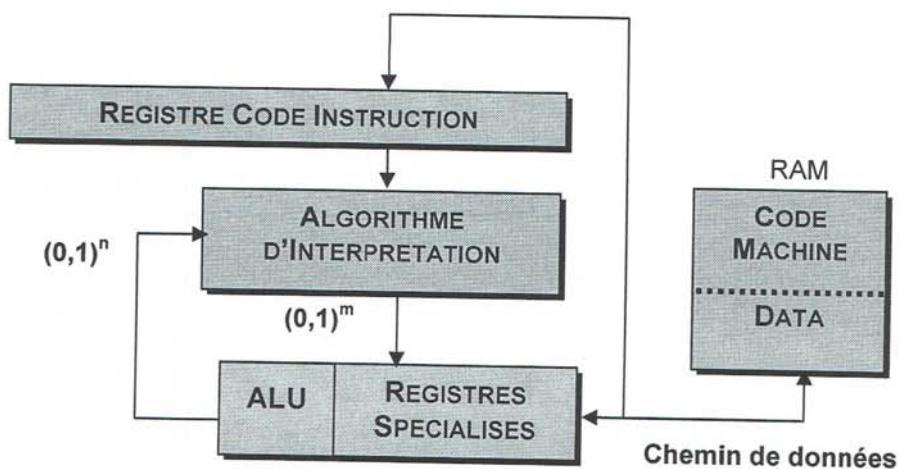

Comme à l'accoutumée une transition dans l'unité de traitement est régie par la commande que lui délivre l'unité de commande, cette dernière apparaît comme un passage obligé. Il est alors nécessaire d'introduire un registre appelé registre code instruction, qui représente une entrée supplémentaire à l'automate de commande, et qui contiendra le code opératoire de l'instruction en code machine à exécuter.

Le code opératoire, contenu dans le registre code instruction, devra être converti en une séquence de commandes appropriées appliquées à l'unité de traitement. Cette conversion est accomplie par le biais d'un algorithme d'interprétation, dont l'unité de commande est le siège. Le microprocesseur se présente ainsi comme une structure où cohabitent au minimum deux niveaux de langage:

- 1- Un langage apparenté à un langage de transfert, décrivant l'algorithme d'interprétation. Il est habituellement appelé Microlangage ou Microprogramme.

- 2- Un langage d'instructions appelé code machine, apparaissant dans la mémoire vive.

Le principe fondamental qui doit être retenu dans un tel système est: L'unité de commande matérialise l'algorithme d'interprétation du répertoire d'instructions. Les automates de commande étudiés auparavant peuvent convenir (automate de Wilkes, automate incrémental, ...).

L'unité de traitement du microprocesseur apparaît habituellement, sur le plan synoptique, sous la forme d'un bloc fonctionnel compact qui réunit toutes les ressources, l'unité arithmétique et logique (ALU), auprès de laquelle on fait figurer seulement les registres spécialisés (accumulateur, registre d'adresse-mémoire, compteur de programme- mémoire,...).

Cette structure d'algorithme d'interprétation est le propre de la technologie classique CISC (Complex Instruction Set Component). Il est nécessaire de citer d'autres types de machines existantes.

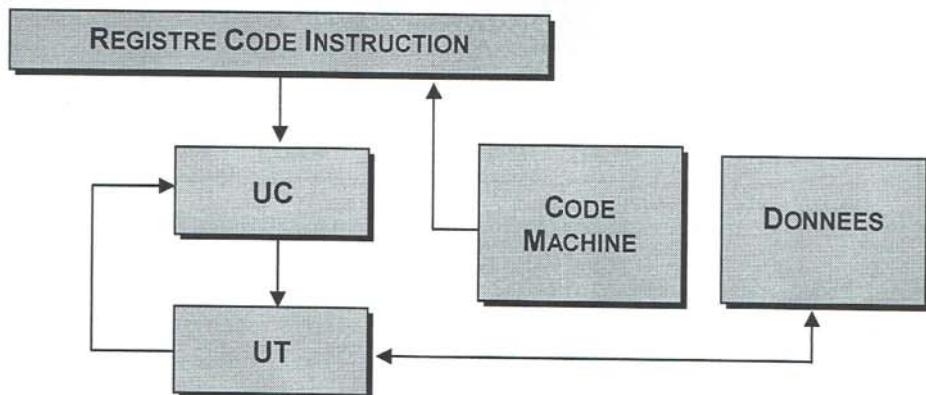

Fig. 11 Le programme-mémoire dans un microprocesseur

Fig. 12 Le microprocesseur représenté par ses deux niveaux de langage

Les machines RISC (Reduced Instruction Set Component), dans lesquelles le micro-code est réduit à l'extrême, ainsi que les machines WISC (Without Instruction Set Component), dans lesquelles il est inexistant. Une architecture autre que celle de Von Neumann est généralement présente sur ces dernières. Il s'agit de l'architecture Harvard qui se distingue par une séparation de la RAM en un champ code instruction et un champ opérande avec chacun son chemin de données propre permettant un gain de temps appréciable dans les accès RAM.

Fig. 13 Architecture Harvard

## VI Appel de sous-programme

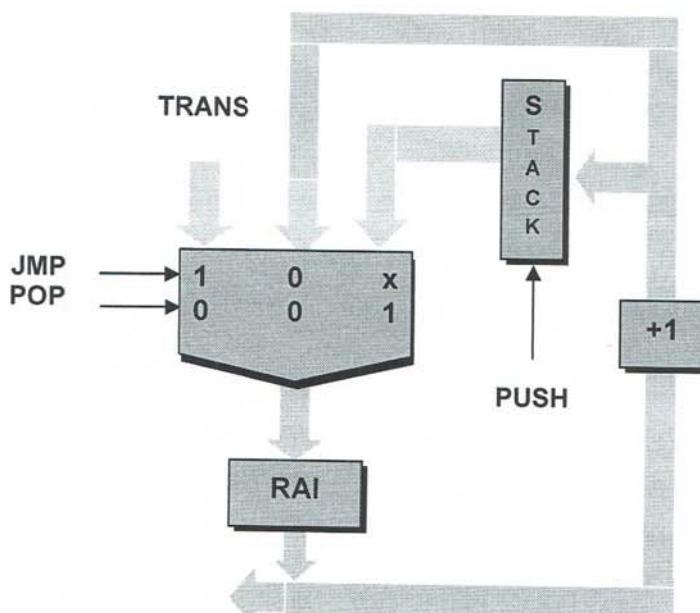

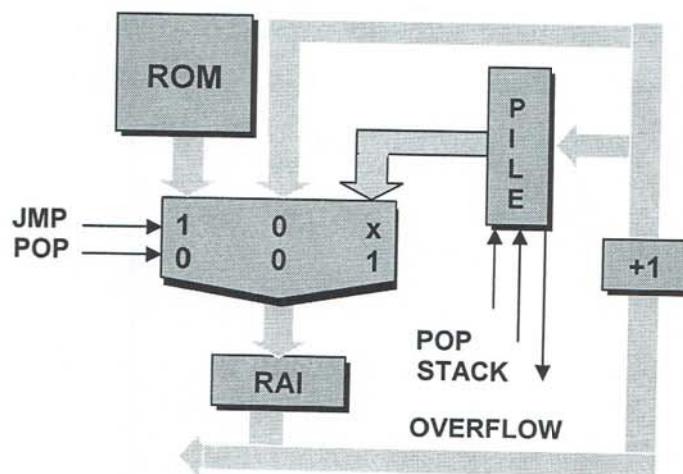

Fig. 14 Séquenceur modifié permettant de faire un appel de sous programme

Le multiplexeur est contrôlé par deux bits notés JMP et POP.

Le chargement du registre STACK s'effectue lorsque le bit PUSH est à 1.

La donnée provenant de la ROM est notée TRANS.

$[RAI]:= [RAI]+1 \rightarrow$  incrémentation du RAI.

$[RAI]:= TRANS \rightarrow$  transition.

$[stack]:=[RAI]+1 \rightarrow$  appel de sous programme avec sauvegarde de l'adresse RAI.

$[RAI]:= [STACK] \rightarrow$  retour de sous programme avec restitution de l'adresse.

Le séquenceur d'automate précédent ne permet de faire qu'un seul appel de sous programme valide. Afin de pouvoir effectuer des appels de sous

programme imbriqués, nous sauvegardons les adresses de retour respectives dans une mémoire vive de type FILO, appelée PILE.

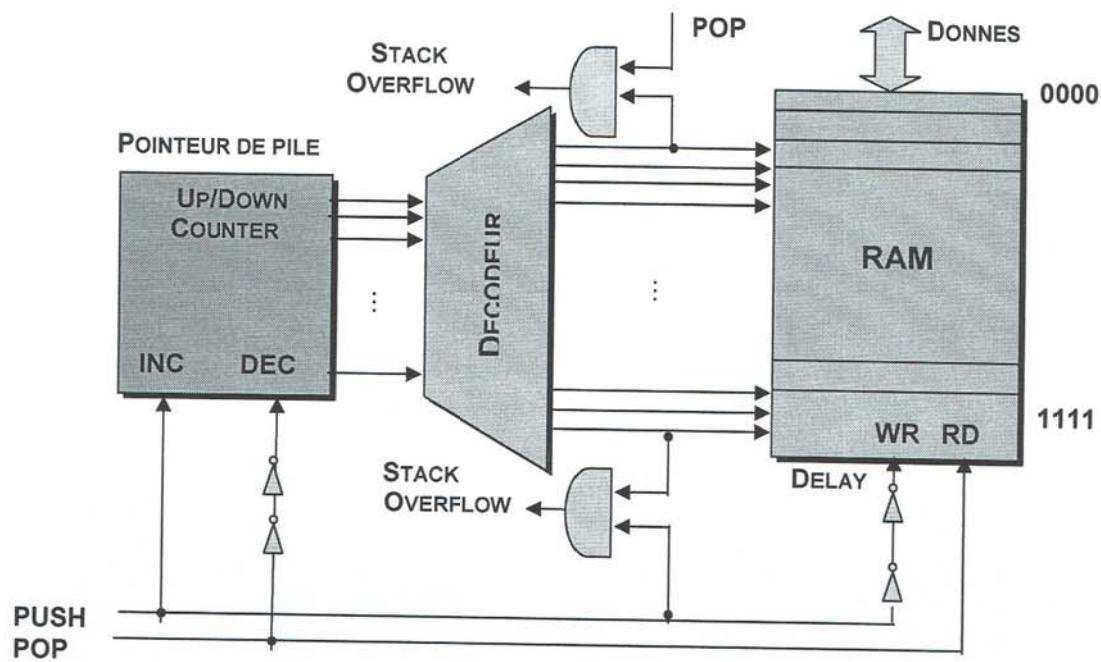

Fig. 15 Schéma de principe d'une Mémoire FILO

### VI.1 Mémoire FILO utilisée comme pile de programme

Fig. 16 Séquenceur modifié permettant de faire plusieurs appels de sous programmes imbriqués

L'opération d'empilement obéit à la séquence: Incrémentation du pointeur de pile, ensuite écriture en RAM.

L'opération de dépilement: Lecture en RAM, puis décrémentation du pointeur.

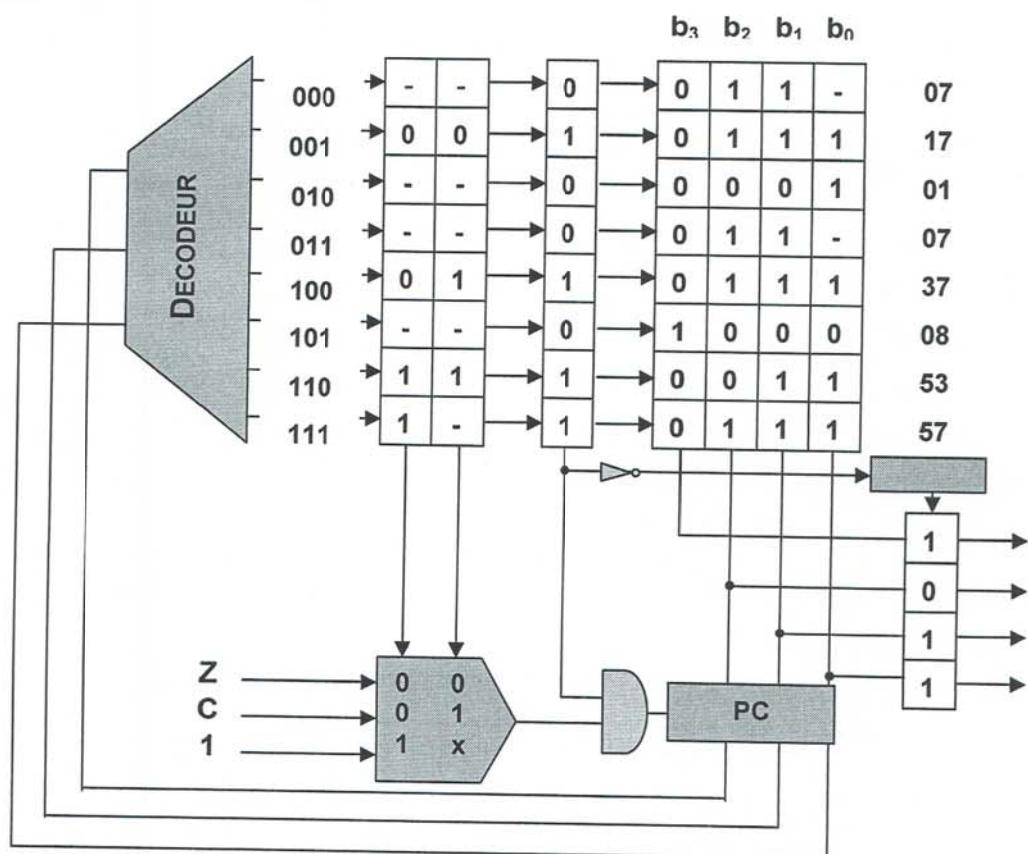

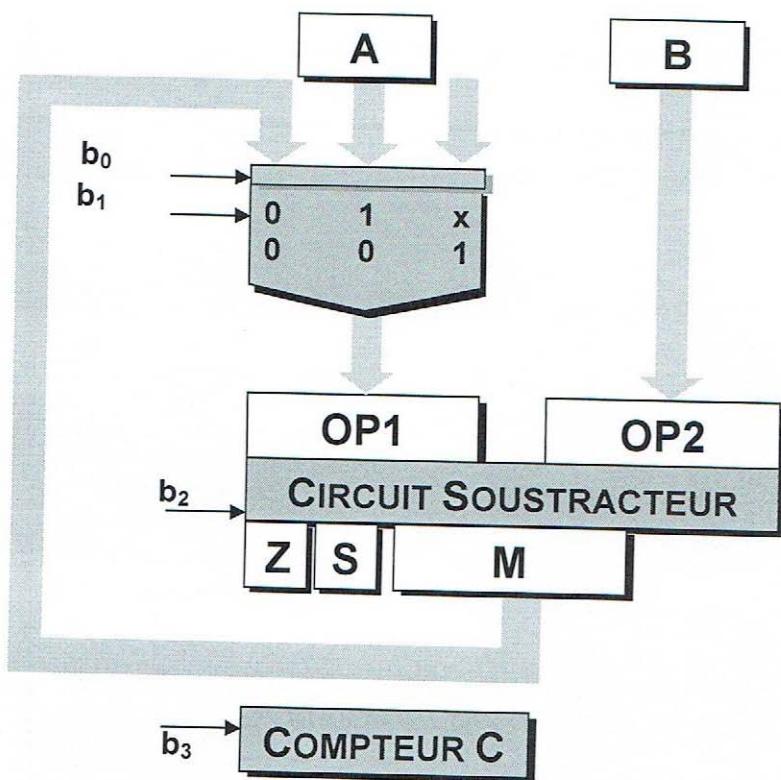

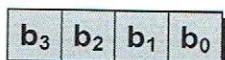

## VII Exemple d'application

### Algorithme de calcul:

Sans rien charger dans OP1'', faire la soustraction OP1-OP2.

Si M=0 fin de calcul (division par zéro).

Sinon charger A dans OP1.

Faire la soustraction OP1-OP2.

Si M<0 fin de calcul (avec Q=C et R=OP1)

Sinon incrémenter C et charger M dans OP1

Allez à 4.

Fin de calcul (automate bloqué dans cette étape).

Il vous est demandé de respecter la structure du mot de commande qui doit être comme suit:

$b_0, b_1$  : Commande du multiplexeur.

$b_2=1$  : Activation du soustracteur.

$b_3=1$  : Activation du compteur.

OP1, S, M et C ont tous pour valeur initiale 0.

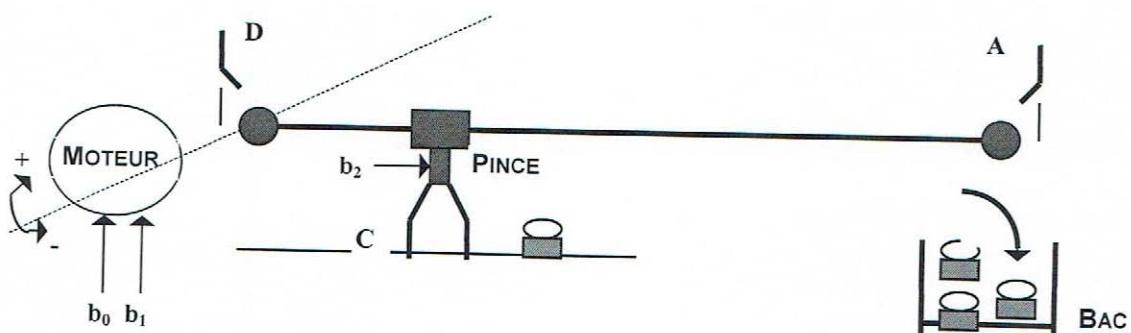

En respectant toutes les données de l'énoncé, réaliser la partie commande de l'automate incrémental qui matérialise cet algorithme. Donner un schéma complet de l'automate ainsi réalisé (partie traitement, partie commande et connexion).

### Solution:

Fig. 17 Unité de commande du circuit de la division

# **CHAPITRE 2**

## **MICRO-ORDINATEUR IBM PC-XT**

### **I Introduction**

La plupart des utilisateurs d'ordinateurs compatibles IBM (Industry Business Machine) n'exploitent sur leur système que les logiciels d'applications. Ils restent ainsi limités à un stade logiciel sans jamais passer au stade matériel. Pourtant, connaître la structure interne d'un ordinateur peut être bénéfique à plus d'un titre à tous ceux qui souhaitent intervenir au niveau matériel sur leur ordinateur que ce soit pour améliorer les performances de la machine ou bien pour concevoir de nouvelles cartes d'extension.

Le premier ordinateur personnel d'IBM mis sur le marché en 1981 était livré avec un microprocesseur 8088 de la firme Intel, une mémoire centrale (mémoire vive ou RAM et mémoire morte ou ROM) allant de 64 K-octets pour le PC junior à 256 K-octets pour les PC-XT, un bus de données de 8 bits, un bus d'adresses de 20 bits, un lecteur de disquettes de 360 K-octets, un BIOS (Basic Input Output System) et un interpréteur BASIC (Beginner's All-purpose Symbolic Instruction Code), tous deux, résidants en mémoire morte et un système d'exploitation MS-DOS (Microsoft Disk Operating System), fourni sur un disque souple. Ce chapitre est consacré à la description succincte des principaux composants du micro-ordinateur IBM PC-XT.

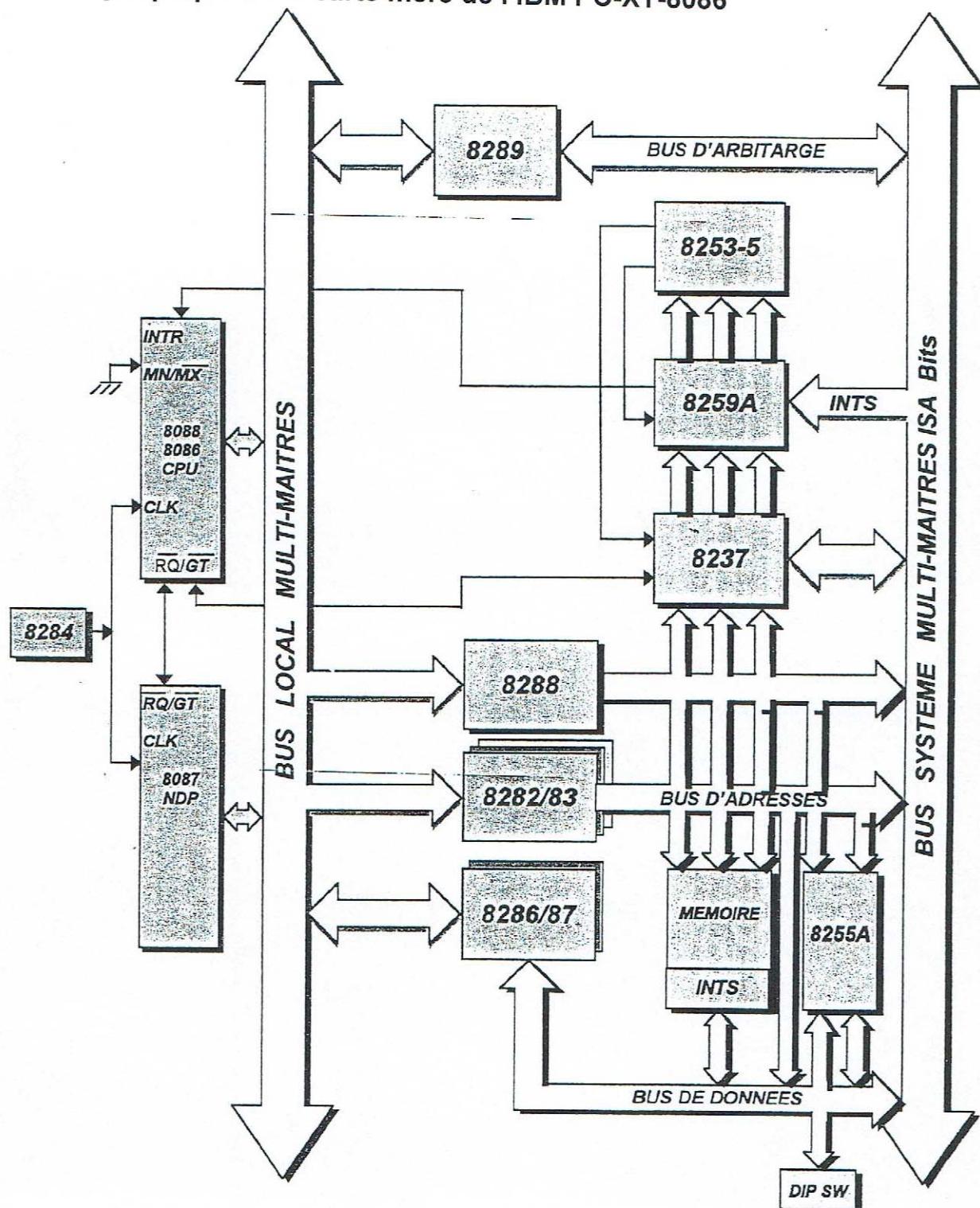

### **II Circuits de la carte mère**

La carte mère est le cœur de l'ordinateur. Elle se trouve généralement en bas du boîtier de l'IBM PC ou bien montée contre le côté dans le boîtier tour. La fonction essentielle de la carte mère est d'assurer harmonieusement la liaison entre tous les éléments qu'elle contient. Chaque élément assure une tâche bien précise. En général, nous y trouvons ce qui suit:

#### **II.1 Microprocesseur**

C'est l'organe principal du micro-ordinateur. Il exécute les logiciels (programmes) et envoie des ordres à son environnement. Les performances globales d'un système dépendent essentiellement du microprocesseur utilisé. Nous consacrerons plusieurs chapitres à l'architecture et à la programmation du microprocesseur 8086 d'Intel.

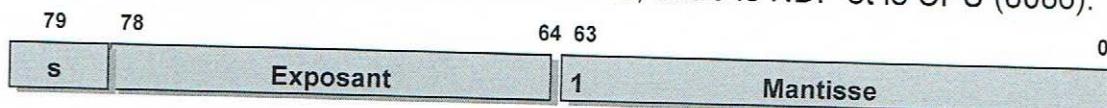

## **II.2 Coprocesseur mathématique**

Le coprocesseur mathématique est spécialisé dans le traitement des nombres à virgule flottante. Il permet donc d'accélérer les opérations arithmétiques en virgules flottantes, les fonctions trigonométriques et logarithmiques. Notons qu'il ne nous est pas possible d'étudier le coprocesseur mathématique du 8086 (architecture et programmation), en l'occurrence le 8087. Néanmoins, nous consacrerons une série de travaux dirigés à l'étude des différentes représentations des nombres dans le 8087.

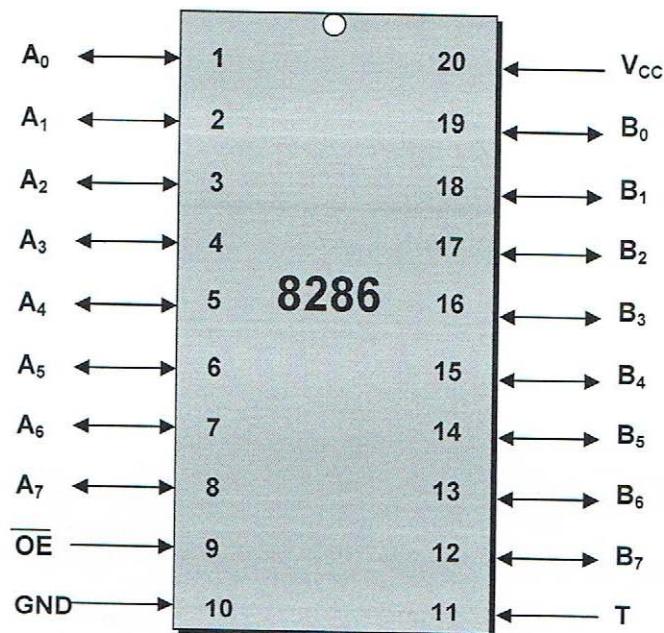

## **II.3 Buffer de données bidirectionnel 8286/8287**

Ce circuit permet d'amplifier, et le cas échéant d'isoler les signaux de données échangés entre le microprocesseur et les mémoires ou entre le microprocesseur et les périphériques d'entrées et sorties. C'est très souvent le circuit équivalent TTL 74/245 qui le remplace sur les carte-mères courantes.

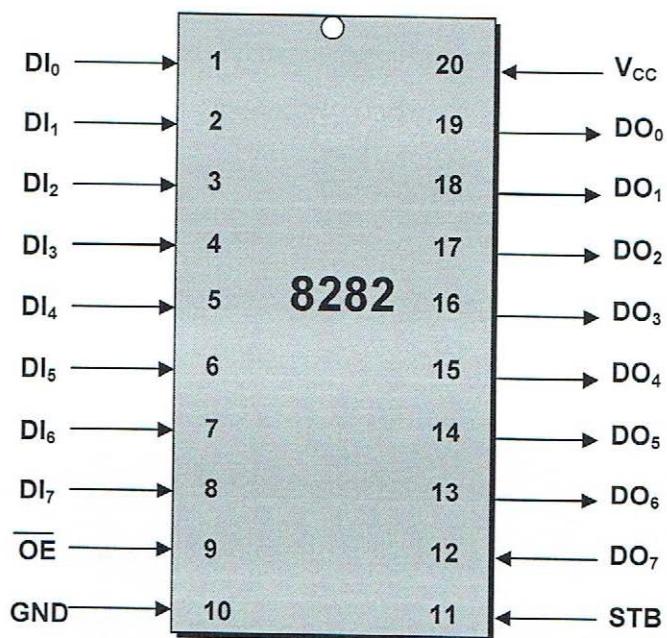

## **II.4 Latch d'adresses 8282**

Ce circuit assure le verrouillage de l'adresse et, par une exploitation judicieuse, le démultiplexage des bus d'adresses et données. C'est très souvent le circuit équivalent TTL 74/373 qui le remplace sur les carte-mères courantes.

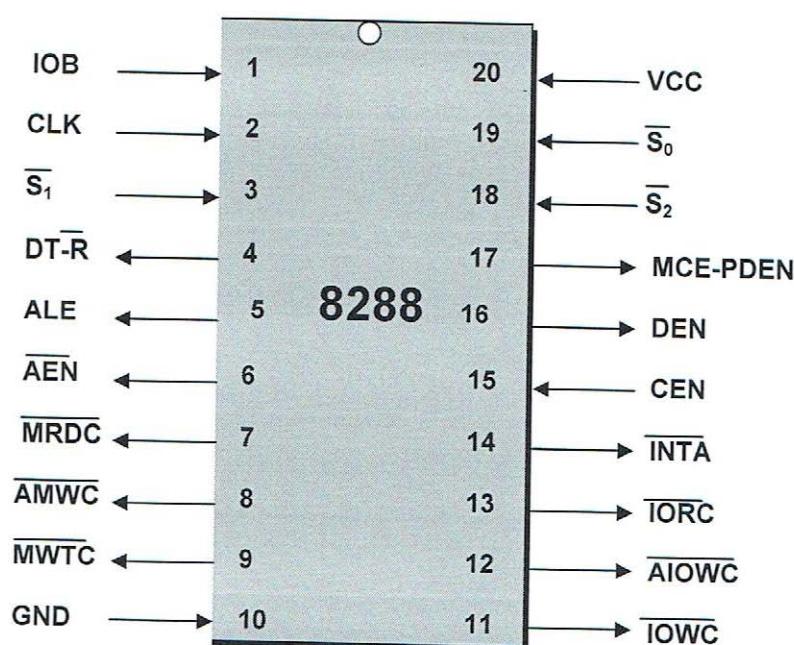

## **II.5 Contrôleur de bus 8288**

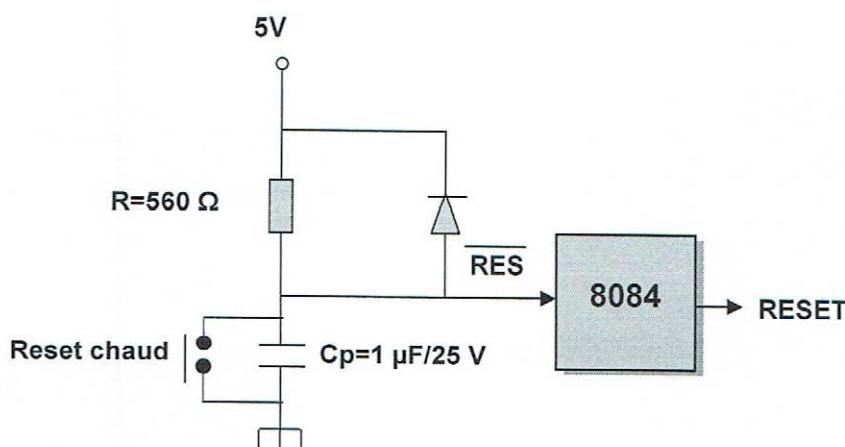

Ce circuit prend à sa charge les signaux de contrôle lors de l'utilisation du microprocesseur en mode maximum. Il assure l'arbitrage de l'utilisation du bus (les bus d'adresses de données et de commandes) dans le cas des configurations à plusieurs maîtres.

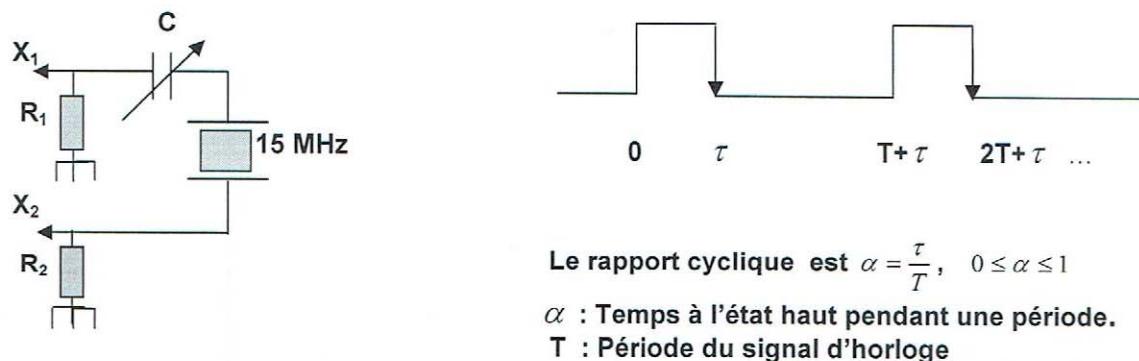

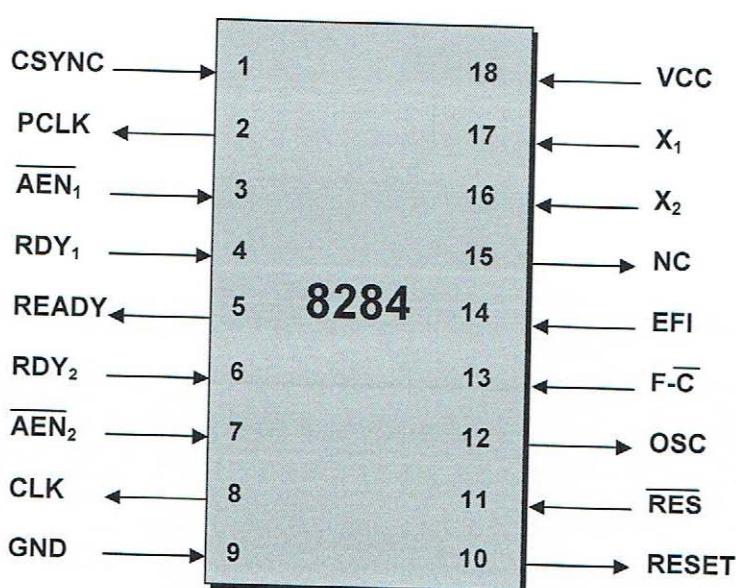

## **II.6 Circuit d'horloge 8284**

C'est ce circuit qui génère l'impulsion d'horloge du microprocesseur 8086. Outre cette fonction, ce circuit joue un rôle prépondérant dans le RESET et la gestion des temps d'attente, comme il sera montré plus loin.

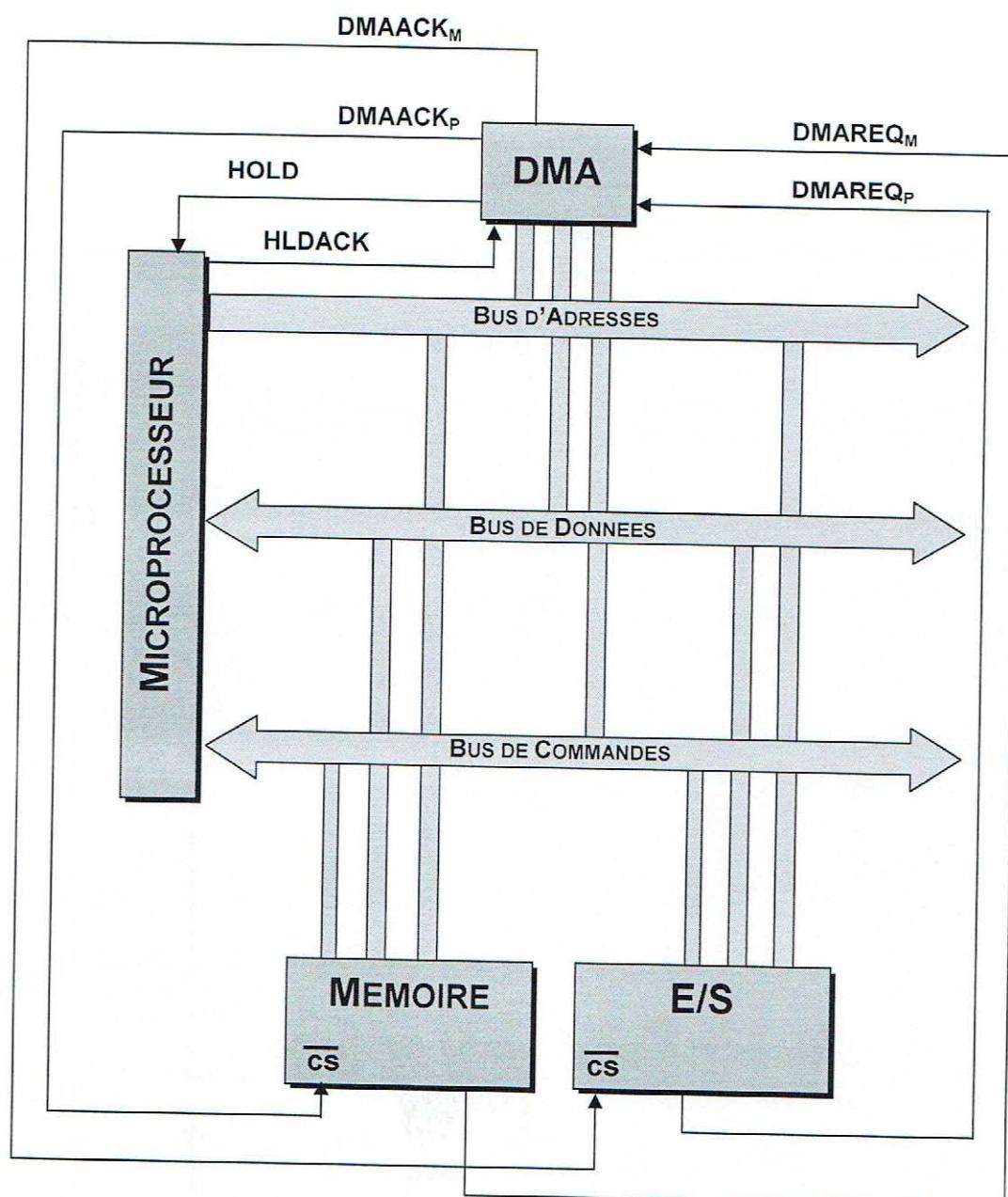

## **II.7 Contrôleur d'accès direct mémoire DMAC 8237**

Le concept d'accès direct mémoire désigne la possibilité de transférer des données entre la mémoire et un périphérique, ou entre deux adresses différentes de la mémoire, sans transiter par les registres internes du microprocesseur. Ceci octroie au transfert des données une augmentation de vitesse considérable. Cette fonctionnalité est rendu possible grâce au concours de circuit contrôleurs DMA, tel

le 8237 d'Intel qui est constitué de quatre canaux identiques et indépendants, numérotés de 0 à 3. Ils sont répartis de la manière donnée par le Tableau 1.

Tableau 1 Répartition des canaux du DMA 8237 sur la carte d'un PC-XT

| Canaux DMA | Fonction sur la carte d'un PC-XT                                                             |

|------------|----------------------------------------------------------------------------------------------|

| 0          | Utilisé pour l'indispensable opération cyclique de rafraîchissement de la mémoire dynamique. |

| 1          | Laissé libre pour une éventuelle application utilisateur.                                    |

| 2          | Affecté aux transferts de données entre la mémoire RAM et les lecteurs de disquettes.        |

| 3          | Affecté aux transferts de données entre la mémoire RAM et le lecteur de disque dur.          |

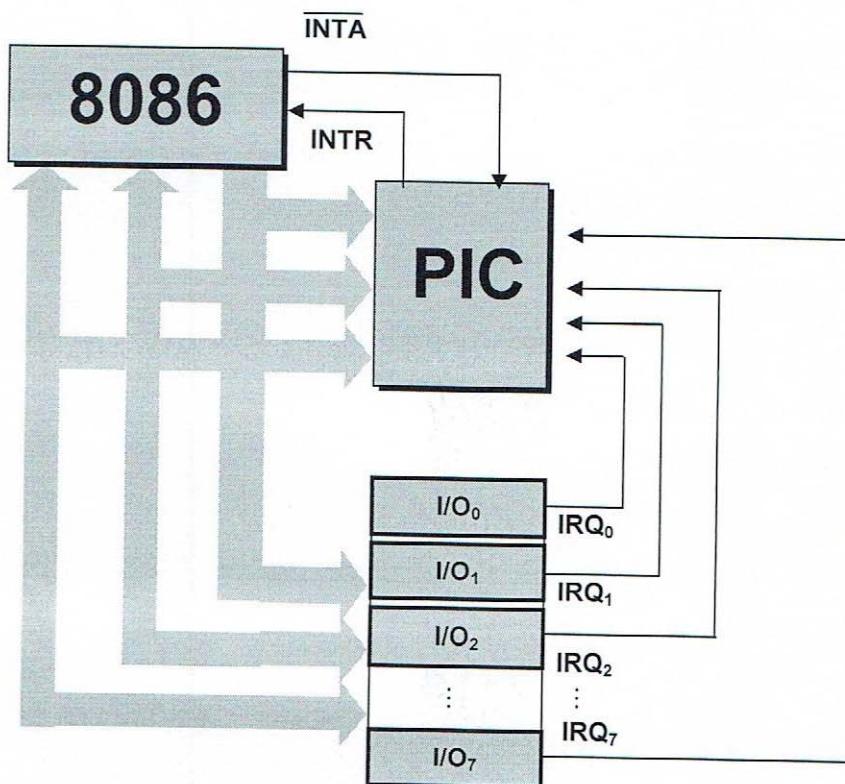

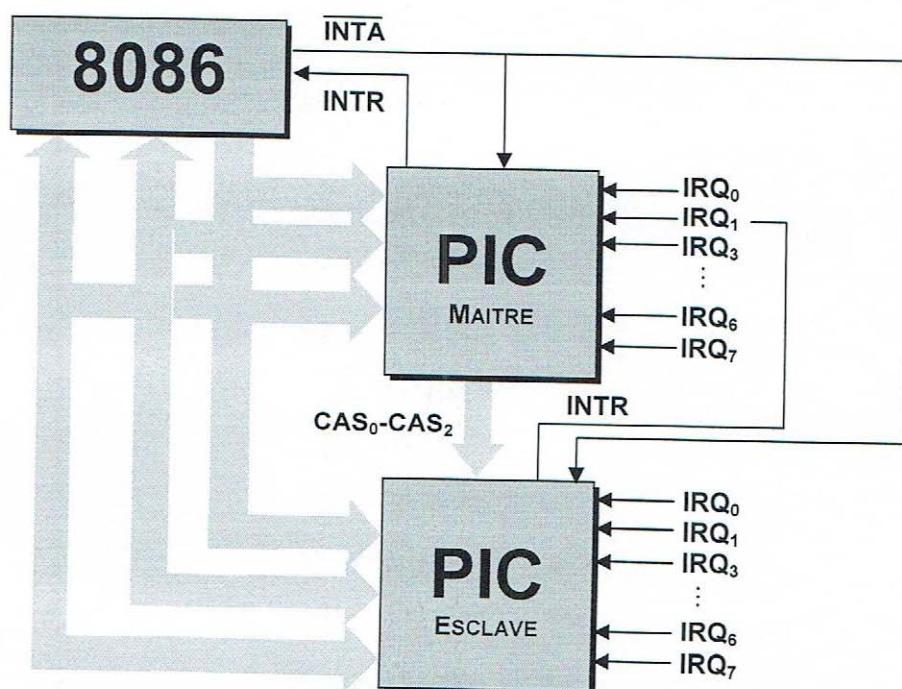

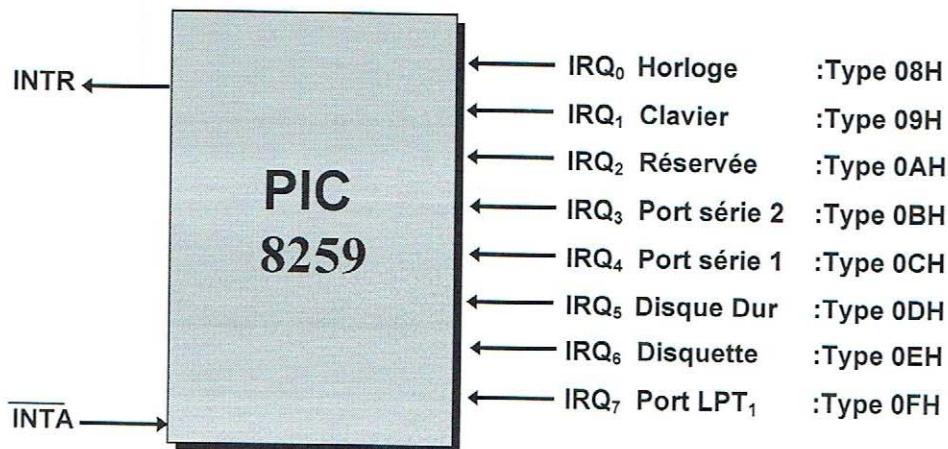

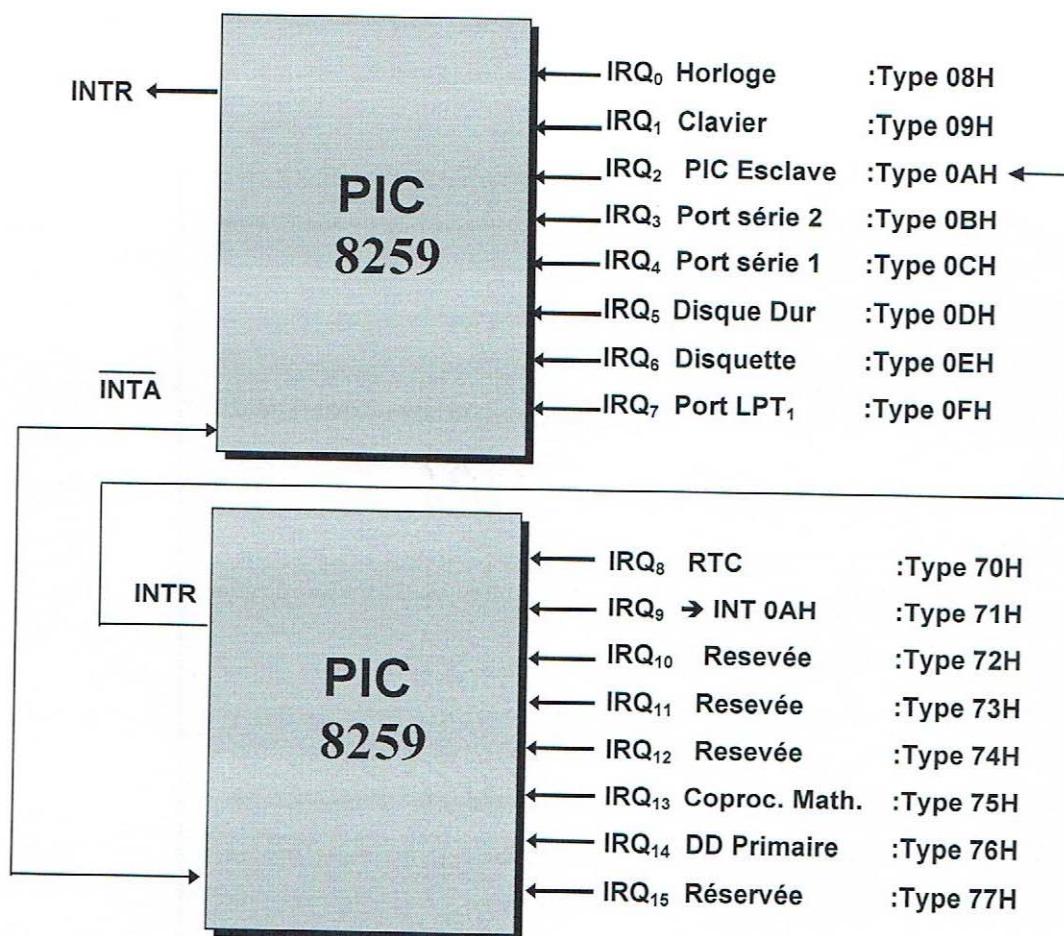

## II.8 Contrôleur d'interruptions programmable PIC 8259

Ce circuit sert à l'identification du périphérique qui sollicite une interruption matérielle du microprocesseur. En cas de demandes simultanées, le 8259 peut arbitrer jusqu'à huit niveaux de priorité, qui sont numérotés par ordre décroissant de  $\text{IRQ}_0, \text{IRQ}_1, \text{IRQ}_2 \dots, \text{IRQ}_7$ . Les périphériques reliés aux entrées du PIC 8259 et leurs fonctions respectives dans un PC-XT sont résumés dans le Tableau 2.

Tableau 2 Périphériques reliés aux entrées du PIC 8259 d'un PC-XT

| Broche $\text{IRQ}_i, i=0,1, 2, \dots 7$ | Périphérique relié à $\text{IRQ}_i$ |

|------------------------------------------|-------------------------------------|

| $\text{IRQ}_0$                           | Tempsiteur-Compteur 8253 (Horloge)  |

| $\text{IRQ}_1$                           | Clavier                             |

| $\text{IRQ}_2$                           | Libre                               |

| $\text{IRQ}_3$                           | Port série 2 ( $\text{COM}_1$ )     |

| $\text{IRQ}_4$                           | Port série 1 ( $\text{COM}_2$ )     |

| $\text{IRQ}_5$                           | Disque dur                          |

| $\text{IRQ}_7$                           | Imprimante ( $\text{LPT}_1$ )       |

Nous reviendrons plus en détail sur le fonctionnement de ce circuit dans le chapitre consacré aux interruptions.

## II.9 Temporisateur-compteur programmable CTC 8253

Ce circuit spécialité rassemble en même temps les caractéristiques des compteurs et des générateurs de signaux, alliées à une grande souplesse d'utilisation du fait de sa commande par logiciel. Il possède trois canaux distincts, numérotés de 0 à 2, pouvant être utilisés séparément en générateur d'impulsions à fréquence programmable, en monostable universel, en compteurs

d'événements, ou en compteur d'intervalle. Ils sont répartis de la manière donnée par le Tableau 3.

Tableau 3 Répartition des canaux du CTC 8253 sur la carte d'un PC-XT

| Canaux CTC | Fonction sur la carte d'un PC-XT                                                                                            |

|------------|-----------------------------------------------------------------------------------------------------------------------------|

| 0          | Utilisé pour générer, toutes les 1/18.2 <sup>ème</sup> de seconde, l'interruption cyclique de l'horloge système via le PIC. |

| 1          | Affecté à déclencher périodiquement au niveau du DMAC le cycle de rafraîchissement de la RAM dynamique.                     |

| 2          | Donne la tonalité pour la génération des sons au niveau du haut-parleur.                                                    |

## II.10 Interface parallèle de périphérique PPI 8255

Ce circuit fait l'objet d'un chapitre consacré aux périphériques à transfert de données en parallèle. Nous nous limiterons dans cette partie introductory à indiquer son utilisation sur un IBM PC-XT en tant qu'interface de communication avec le clavier en premier lieu, et en tant que tampon de lecture des indicateurs de configuration en second lieu. En outre, il assure l'activation ou l'inhibition de la ligne de connexion entre le temporisateur-compteur 8253 et le haut-parleur.

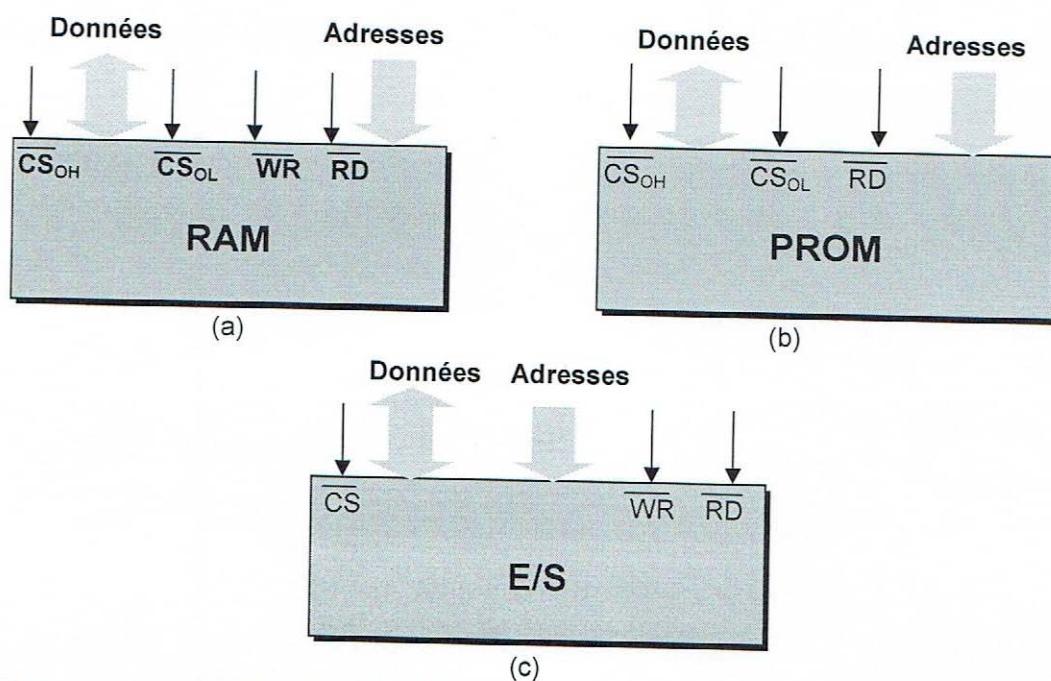

## II.11 Mémoire centrale

Les PC-XT (Extended Technology), à base du 8086, pouvaient gérer jusqu'à 1 Mo mémoire, réparti selon le Tableau 4. Le MS-DOS (Micro Soft Disk Operating System) utilisait 640 Ko de mémoire conventionnelle (Base Memory) uniquement. Les 384 Ko de mémoire supérieure LIM (Lotus Intel Motorola en circuits intégrés) ou EMS (Expanded Memory System) étaient utilisés par la mémoire écran, le BIOS (Basic Input Output System), le BIOS du disque dur et la carte graphique EGA (Enhanced Graphic Adapter).

Les PC-AT (Advanced Technology), à partir du microprocesseur 80286 gèrent au minimum 16 Mo mémoire. La zone supérieure à 1 Mo est appelée mémoire étendue ou XMS (Extended Memory System), car elle correspond aux cases mémoire accessibles grâce au bus d'adresses. La mémoire EMS en circuits intégrés a, quant à elle, disparue.

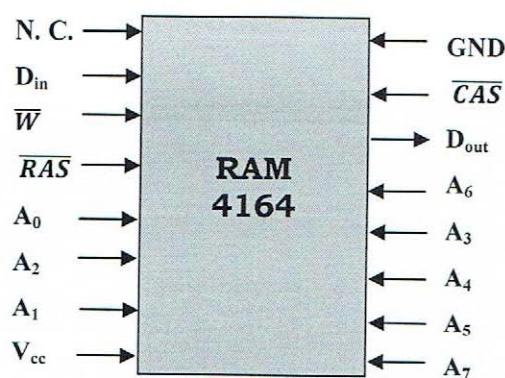

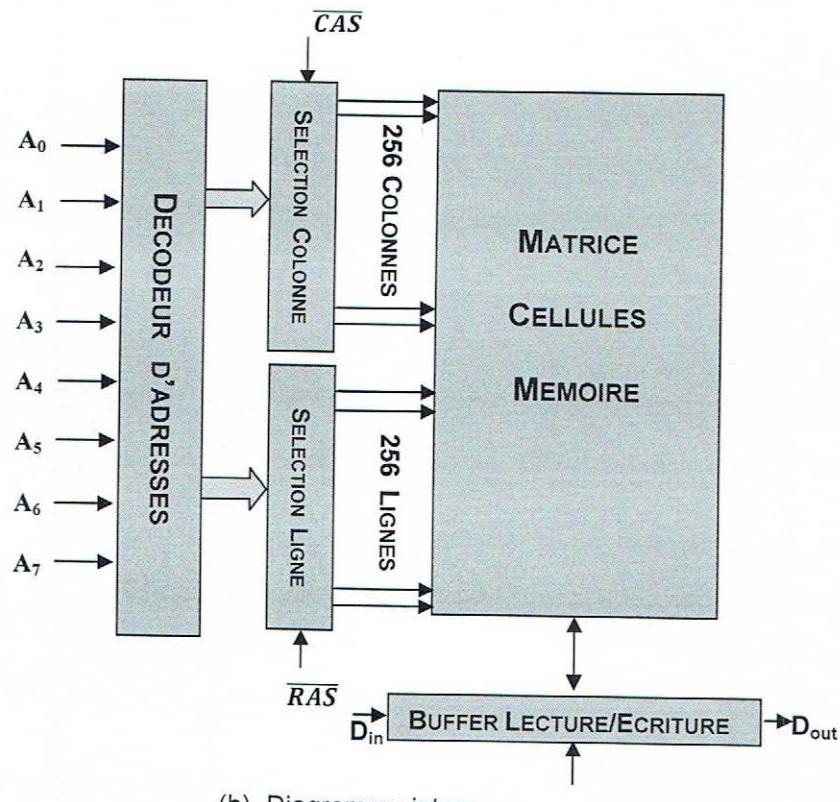

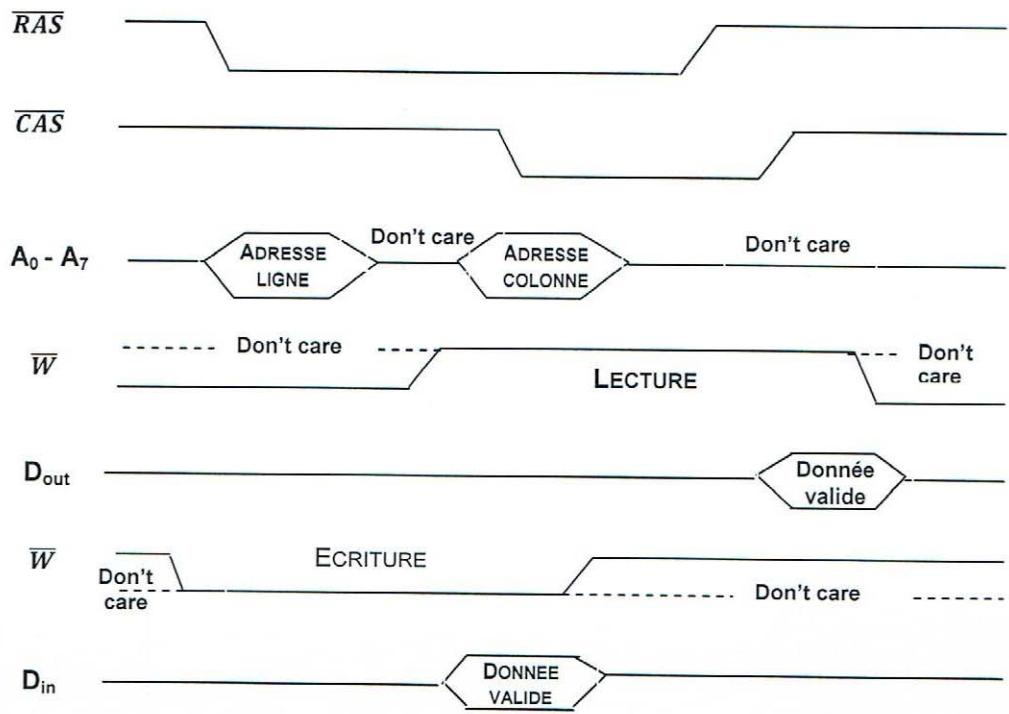

### II.11.1 Mémoire RAM dynamique

Le PC est sorti avec une mémoire vive de 64 K-octets en 1981 sur un total de 640 K-octets atteint ultérieurement. La RAM dynamique contient les programmes et les données en cours d'exécution et une partie du système d'exploitation.

## II.11.2 Mémoire morte ROM

Elle contient le BIOS: fonctions primitives nécessaires au système d'exploitation. C'est aussi le support physique du programme qui assure la prise en charge des opérations de démarrage du système, y compris la vérification de la configuration matérielle et le diagnostique.

## II.12 Indicateurs de configuration matérielle

Il s'agit d'un ensemble de huit interrupteurs dont la position représente une information codée concernant le nombre d'unités de disquettes présentes sur la machine, la présence du coprocesseur arithmétique 8087, la quantité de RAM et le type de carte vidéo. Le système d'exploitation fait une lecture automatique de ces indicateurs lors de la mise sous tension.

Très rapidement, ces interrupteurs ont été supplantés par la mémoire MC6818 ou RTC/CMOS RAM (Real Time Clock/Static Complementary Metal Oxyde Semi-Conductor), circuit qui réunit sur la même puce un calendrier en temps réel et une RAM statique pour la conservation des paramètres de configuration matérielle. Le programme "SETUP" d'exploitation de la RTC/CMOS se trouve en ROM-BIOS.

Tableau 4 Organisation de la mémoire d'un PC

| Bloc | Adresse                   | Contenu                            |

|------|---------------------------|------------------------------------|

| 15   | F000 : 0000 – F000 : FFFF | BIOS                               |

| 14   | E000 : 0000 – E000 : FFFF | Libre pour insertion d'une ROM     |

| 13   | D000 : 0000 – D000 : FFFF | Libre pour insertion d'une ROM     |

| 12   | C000 : 0000 – C000 : FFFF | ROM BIOS supplémentaire            |

| 11   | B000 : 0000 – B000 : FFFF | RAM d'écran                        |

| 10   | A000 : 0000 – A000 : FFFF | RAM d'écran EGA / VGA              |

| 9    | 9000 : 0000 – 9000 : FFFF | RAM de 576 K octets à 640 K octets |

| 8    | 8000 : 0000 – 8000 : FFFF | RAM de 512 K octets à 576 K octets |

| 7    | 7000 : 0000 – 7000 : FFFF | RAM de 448 K octets à 512 K octets |

| 6    | 6000 : 0000 – 6000 : FFFF | RAM de 384 K octets à 448 K octets |

| 5    | 5000 : 0000 – 5000 : FFFF | RAM de 320 K octets à 384 K octets |

| 4    | 4000 : 0000 – 4000 : FFFF | RAM de 256 K octets à 320 K octets |

| 3    | 3000 : 0000 – 3000 : FFFF | RAM de 192 K octets à 256 K octets |

| 2    | 2000 : 0000 – 2000 : FFFF | RAM de 128 K octets à 192 K octets |

| 1    | 1000 : 0000 – 1000 : FFFF | RAM de 64 K octets à 128 K octets  |

| 0    | 0000 : 0000 – 0000 : FFFF | RAM de 0 K octets à 64 K octets    |

### **III Cartes d'extensions**

Les cartes d'extension jouent un rôle important dans la gestion des périphériques. Dans un contexte PC-XT, les adresses de leurs ports d'entrées et sorties sont résumées dans le Tableau 5. Dans ce qui suit, nous les décrivons laconiquement.

#### **III.1 Carte graphique**

Son rôle consiste à lire les données envoyées sous forme digitale par le processeur central, à les convertir en signaux analogiques, et à les transmettre par un câble au moniteur qui les traduira en image. Son élément central est le contrôleur d'écran CRTC MC 6845 (Cathod Ray Tube Controller) circuit qui permet les deux modes d'utilisation de l'écran, le mode texte et le mode graphique.

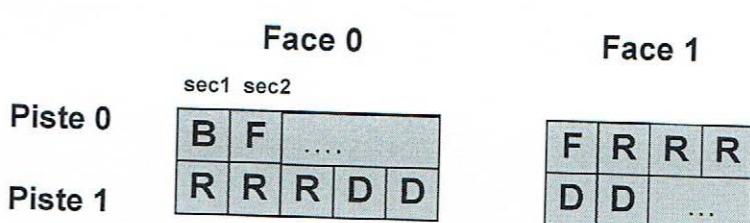

#### **III.2 Contrôleur de lecteurs de disquettes FDC 8272**

Le 8272 d'Intel est un contrôleur de disquettes (FDC, Floppy Disk Controller) en technologie LSI (Large Scale Integration, pouvant prendre entre 100 et 5000 circuits élémentaires) contenant les circuits et les fonctions de contrôle nécessaires pour réaliser l'interface entre un processeur et quatre lecteurs de disquettes. Il est capable de supporter soit le format simple densité (FM, Frequency Modulation) d'IBM 3740 (Data Entry System), ou le format double densité (MFM, Modified Frequency Modulation) d'IBM système 34 (minicomputer d'IBM de 1978 à 1983) avec enregistrement double faces. Les 8272 donne les signaux qui simplifient la conception d'une boucle à verrouillage de phase (PLL, Phase Locked Loop) externe et le circuit de précompensation en écriture. La PLL a pour utilité l'asservissement de la fréquence des signaux dans le cas de perturbation de la vitesse de rotation du moteur du lecteur de disquettes. La première disquette d'IBM (1971) était de capacité 81.6 K Octets (32 pistes). Six ans plus tard, une disquette de capacité 1.2 M Octets (154 pistes) a vu le jour.

La précompensation, quant à elle désigne une mesure introduite afin de pallier à la distorsion magnétique qui affecte les signaux enregistrés sur les pistes les plus internes de la disquette.

#### **III.3 Port série et le port parallèle**

C'est souvent sur la même carte que sont présents l'UART 8250, circuit d'interface avec le port série RS-232, et l'interface parallèle Centronics dont l'utilisation principale sur l'IBM-PC est la connexion avec l'imprimante. Ces deux standards d'interfaces feront l'objet de chapitres séparés.

### III.4 Clavier

Le clavier fournit les données en série. Il possède son propre microprocesseur 8042 qui permet de diagnostiquer l'état du clavier à la mise sous tension, de générer le code des touches du clavier (scan code) et de le transmettre au tampon mémoire de la carte mère qui peut contenir un maximum de 14 caractères.

Tableau 5 Standardisation des adresses des ports d'entrées et sorties

| Circuit                                        | PC-XT     | PC-AT     |

|------------------------------------------------|-----------|-----------|

| Contrôleur DMA n° 1 (8237A-5)                  | 000 – 00F | 000 – 01F |

| Contrôleur d'interruption n° 1 PIC (8259A)     | 020 – 021 | 020 – 03F |

| Temporisateur CTC (8253)                       | 040 – 043 | 040 – 05F |

| Interface parallèle de périphérique PPI (8255) | 060 – 063 | Néant     |

| Clavier (8042)                                 | Néant     | 060 – 06F |

| Horloge temps réel RTC/CMOS (MC6818)           | Néant     | 070 – 07F |

| Registre de page DMA                           | 080 – 083 | 080 – 09F |

| Contrôleur d'interruption n° 2 PIC (8259A)     | Néant     | 0A0 – 0BF |

| Contrôleur DMA n° 2 (8237A-5)                  | Néant     | 0C0 – 0DF |

| Coprocesseur arithmétique                      | Néant     | 0F0 – 0F1 |

| Coprocesseur arithmétique                      | Néant     | 0F8 – OFF |

| Contrôleur de disque dur                       | 032 – 32F | 1F0 – 1F8 |

| Manette de jeux                                | 200 – 20F | 200 – 207 |

| Unité d'extension                              | 210 – 217 | Néant     |

| Imprimante parallèle n° 2                      | Néant     | 278 – 27F |

| Interface série n° 2                           | 2F8 – 2FF | 2F8 – 2FF |

| Carte prototype                                | 300 – 31F | 300 – 31F |

| Carte réseau                                   | Néant     | 360 – 36F |

| Imprimante parallèle n° 1                      | 378 – 37F | 378 – 37F |

| Carte écran monochrome                         | 3B0 – 3BF | 3B0 – 3BF |

| Carte vidéo couleur graphique                  | 0D0 – 0DF | 0D0 – 3DF |

| Contrôleur de disquettes                       | 3F0 – 3F7 | 3F0 – 3F7 |

| Interface série n° 1                           | 3F8 – 3FF | 3F8 – 3FF |

### III.5 Connecteurs du bus ou slots d'extensions

Ces connecteurs ou slots sont mis à la disposition de l'utilisateur pour d'éventuels ajouts de périphériques. Ils représentent un support visible du bus système, avec le bus d'adresses et le bus de données démultiplexés, ainsi que toutes les lignes du bus de contrôle séparées. Sur les IBM PC-XT nous avons des bus sur le standard ISA (Industry Standard Architecture). Le Tableau 6 résume la fonction de

chacun des signaux constituant le slot ou connecteur à 62 broches de ce bus d'extension pour les PC-XT.

Tableau 6 Connecteur d'extension à 62 broches

| Broche                            | Signal                           | E/S | Fonction                 |

|-----------------------------------|----------------------------------|-----|--------------------------|

| A <sub>1</sub>                    | I/O CH CK                        | E   | I/O Channel Check        |

| A <sub>2</sub> à A <sub>9</sub>   | D <sub>7</sub> à D <sub>0</sub>  | E/S | Data Bus                 |

| A <sub>10</sub>                   | I/O CH RDY                       | E   | I/O Channel Ready        |

| A <sub>11</sub>                   | AEN                              | S   | Address Enable (for DMA) |

| A <sub>12</sub> à A <sub>31</sub> | A <sub>19</sub> à A <sub>0</sub> | S   | Address Bus              |

| B <sub>1</sub>                    | GND                              | E   | Ground                   |

| B <sub>2</sub>                    | RESET DRV                        | S   | Reset Driver             |

| B <sub>3</sub>                    | +5V                              | S   | Power                    |

| B <sub>4</sub>                    | IRQ <sub>2</sub>                 | E   | Interrupt Request N° 2   |

| B <sub>5</sub>                    | -5V                              | E   | Power                    |

| B <sub>6</sub>                    | DRQ <sub>2</sub>                 | E   | DMA Request N° 2         |

| B <sub>7</sub>                    | -12V                             | S   | Power                    |

| B <sub>8</sub>                    | Reserved                         | S   | Reserved                 |

| B <sub>9</sub>                    | +12V                             | S   | Power                    |

| B <sub>10</sub>                   | GND                              | -   | Ground                   |

| B <sub>11</sub>                   | MEMW                             | S   | Memory Write             |

| B <sub>12</sub>                   | MEMR                             | S   | Memory Read              |

| B <sub>13</sub>                   | IOW                              | S   | I/O Write                |

| B <sub>14</sub>                   | IOR                              | S   | I/O Read                 |

| B <sub>15</sub>                   | DACK <sub>3</sub>                | S   | DMA Acknowledge N° 3     |

| B <sub>16</sub>                   | DRQ <sub>3</sub>                 | E   | DMA Request N° 3         |

| B <sub>17</sub>                   | DACK <sub>1</sub>                | S   | DMA Acknowledge N° 1     |

| B <sub>18</sub>                   | DRQ <sub>1</sub>                 | E   | DMA Request N° 1         |

| B <sub>19</sub>                   | DACK <sub>0</sub>                | S   | DMA Acknowledge N° 0     |

| B <sub>20</sub>                   | CLOCK                            | S   | 4.77 MHz Clock           |

| B <sub>21</sub>                   | IRQ <sub>7</sub>                 | E   | Interrupt Request N° 7   |

| B <sub>22</sub>                   | IRQ <sub>6</sub>                 | E   | Interrupt Request N° 6   |

| B <sub>23</sub>                   | IRQ <sub>5</sub>                 | E   | Interrupt Request N° 5   |

| B <sub>24</sub>                   | IRQ <sub>4</sub>                 | E   | Interrupt Request N° 4   |

| B <sub>25</sub>                   | IRQ <sub>3</sub>                 | E   | Interrupt Request N° 3   |

| B <sub>26</sub>                   | DACK <sub>2</sub>                | S   | DMA Acknowledge N° 2     |

| B <sub>27</sub>                   | T / C                            | S   | Terminal Count (for DMA) |

| B <sub>28</sub>                   | ALE                              | S   | Address Latch Enable     |

| B <sub>29</sub>                   | +5V                              | S   | Power                    |

| B <sub>30</sub>                   | OSC                              | S   | Oscillator               |

| B <sub>31</sub>                   | GND                              | -   | Ground                   |

Afin d'assurer une compatibilité ascendante, l'IBM PC-AT est équipé du même connecteur ou slot d'extension, et ce pour garantir la connectivité des cartes à 8 bits conçues pour les PC-XT. Il est complété par un second connecteur de 36 broches, Tableau 7, incluant 8 bits de données supplémentaires (portant

ainsi le nombre de fils de données à 16), 4 bits d'adresses supplémentaires (portant ainsi le nombre de fils d'adresses à 24) et certaines autres broches de contrôle propres aux PC-AT.

Tableau 7 Connecteur d'extension à 36 broches

| Broche                            | Signal                              | E/S | Fonction               |

|-----------------------------------|-------------------------------------|-----|------------------------|

| C <sub>1</sub>                    | SBHE                                | E/S | System Bus High Enable |

| C <sub>2</sub> à C <sub>8</sub>   | LA <sub>23</sub> à LA <sub>17</sub> | E/S | Address Bus            |

| C <sub>9</sub>                    | MEMR                                | E/S | Memory Read            |

| C <sub>19</sub>                   | MEMW                                | E/S | Memory Write           |

| C <sub>11</sub> à C <sub>18</sub> | SD <sub>8</sub> à SD <sub>15</sub>  | E/S | Data Bus               |

| D <sub>1</sub>                    | MEM-CS16                            | E   | MEM CS16               |

| D <sub>2</sub>                    | I/O-CS16                            | E   | I/O_CS16               |

| D <sub>3</sub>                    | IRQ <sub>10</sub>                   | E   | Interrupt Request N°10 |

| D <sub>4</sub>                    | IRQ <sub>11</sub>                   | E   | Interrupt Request N°11 |

| D <sub>5</sub>                    | IRQ <sub>12</sub>                   | E   | Interrupt Request N°12 |

| D <sub>6</sub>                    | IRQ <sub>13</sub>                   | E   | Interrupt Request N°13 |

| D <sub>7</sub>                    | IRQ <sub>14</sub>                   | E   | Interrupt Request N°14 |

| D <sub>8</sub>                    | DACK <sub>0</sub>                   | S   | DMA Acknowledge N°0    |

| D <sub>9</sub>                    | DRQ <sub>0</sub>                    | E   | DMA Request N°0        |

| D <sub>10</sub>                   | DACK <sub>5</sub>                   | S   | DMA Acknowledge N°5    |

| D <sub>11</sub>                   | DRQ <sub>5</sub>                    | E   | DMA Request N°5        |

| D <sub>12</sub>                   | DACK <sub>6</sub>                   | S   | DMA Acknowledge N°6    |

| D <sub>13</sub>                   | DRQ <sub>6</sub>                    | E   | DMA Request N°6        |

| D <sub>14</sub>                   | DACK <sub>7</sub>                   | S   | DMA Acknowledge N°7    |

| D <sub>15</sub>                   | DRQ <sub>7</sub>                    | E   | DMA Request N°7        |

| D <sub>16</sub>                   | +5V                                 | -   | Power                  |

| D <sub>17</sub>                   | MASTER                              | E   | Master                 |

| D <sub>18</sub>                   | GND                                 | -   | Ground                 |

#### IV Alimentation

L'alimentation transforme les 220 Volts du secteur en 5 Volts et 12 Volts. Les 5 Volts sont destinés aux circuits de l'ordinateur, alors que les 12 Volts servent à alimenter les moteurs de lecteurs de disquettes et de disques durs. La puissance de sortie de l'alimentation est fonction du nombre de périphériques connectés.

Ainsi, les premiers PC (jusqu'au 8086) disposaient d'une alimentation d'une puissance de 65 Watts permettant d'alimenter l'ensemble des circuits de la carte mère et deux lecteurs de disquettes. Les PC-XT (à partir du 80286) étaient dotés d'une alimentation de type AT d'une puissance de 133 Watts pouvant alimenter, en outre, un disque dur. Avec l'avènement du Pentium II, les PC-AT, ont bénéficié, quant à eux, d'une alimentation de type ATX (Advanced Technology Extended) d'une puissance allant de 220 Volts à 230 Volts. Cette dernière servait aussi à alimenter l'écran et toutes les cartes d'extension.

# CHAPITRE 3

## EVOLUTION DES MICRO-ORDINATEURS PC

### I Introduction

Lorsque Gordon Moore, co-fondateur d'Intel, avait prédit en 1965 que la densité en transistors des circuits intégrés allait doubler tous les deux ans, savait-il que sa prédiction allait se confirmer avec une précision inouïe jusqu'à aujourd'hui? Nous constaterons qu'entre temps la vitesse des calculateurs a augmenté à peu près au même rythme que l'accroissement du taux d'intégration.

En 1971, Intel surprend toute la planète en lançant le premier microprocesseur 4 bits. Il s'agissait du 4004 (2300 transistors et 60000 instructions par seconde). Depuis, on ne le répétera jamais assez, Intel n'arrête pas de créer l'événement en annonçant régulièrement de nouveaux produits toujours plus performants et en honorant ses annonces.

Pour une technologie en perpétuel mouvement nous ne pouvons nous donner la prétention de rendre fait de l'état de l'art, et notre exposé se veut avant tout didactique. Notre choix s'est donc délibérément porté sur le microprocesseur 8086 d'Intel. En effet celui-ci, au même titre que les machines IBM PC-XT qui en sont équipées, réunit dans une large mesure toute la théorie moderne des machines universelles telle qu'elle a été formulée par Johannes Von Neumann (1945).

Par ailleurs, de part sa compatibilité ascendante, il constituera un outil d'apprentissage idéal où l'application pratique peut se réaliser sur n'importe quelle machine de fabrication ultérieure dans un parc très largement doté. S'il nous sera reproché à juste titre que l'exposé reste incomplet non pas relativement au phénomène de mode, mais du fait des limites théoriques imposées par la structure même de l'IBM PC-XT (absence du concept de la mémoire cache, des Vidéo RAM et shadowing, interfaces multimédia, ....) nous renvoyons à ce sujet le lecteur intéressé à la littérature spécialisée. Néanmoins, pour orienter les curieux et assouvir la faim des insatiables, nous présentons, dans ce qui suit, un aperçu succinct de l'évolution vertigineuse de la technologie des micro-ordinateurs de la famille Intel et des différents chipset, bus, interfaces, mémoires et disques durs actuels.

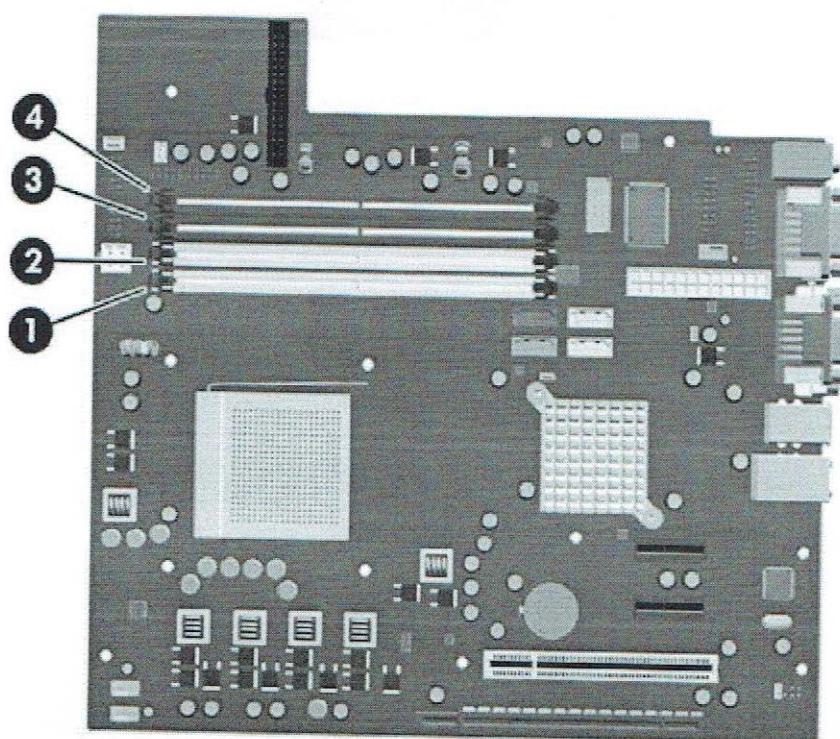

## II Bus

Le bus ISA reste l'un des standards les plus répandus en matière de bus. Ce bus est apparu sous sa première version en 1984 avec le microordinateur IBM PC-AT. Le microprocesseur était alors le 80286 fonctionnant à 8 MHz. Les bus, comme tous les autres composants ont également suivi une évolution historique, passant ainsi du bus ISA du PC-AT aux bus EISA, MCA, VLB, PCI, AGP, USB, PCI, Express, etc.

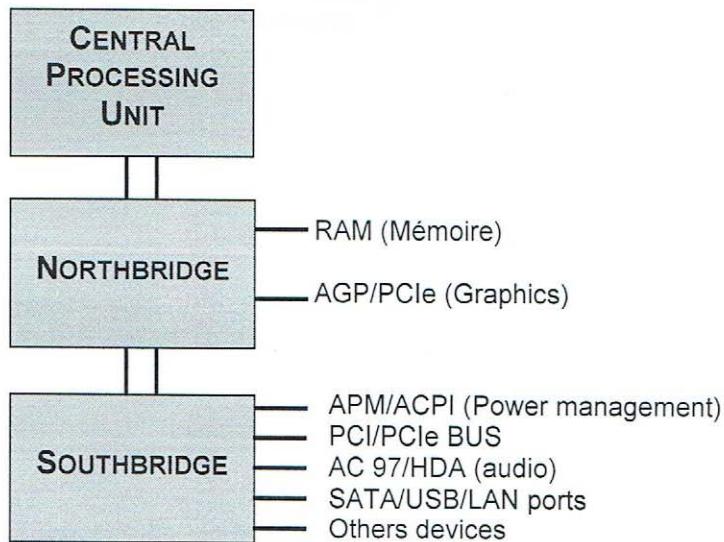

Actuellement, le PCI Express ou PCIe dans sa deuxième version est suffisamment rapide pour remplacer non seulement le PCI classique mais aussi l'AGP, un port rapide exclusivement utilisé pour les cartes graphiques. Dans un avenir proche, il serait même envisagé d'y connecter des périphériques externes. Contrairement au PCI qui est relié au southbridge de la carte mère, le PCIe est relié au northbridge. De plus, alors que le PCI 2.3 (2002) utilise un unique bus de 64 bits bidirectionnel alterné (half duplex) pour tous les périphériques, le PCIe utilise une interface série de 1 bit, à base de lignes bidirectionnelles. Nous pouvons, par exemple, parler d'une carte mère possédant 20 lignes PCIe. Une ligne permet des échanges par ligne et par direction à 250 Mo/s pour le PCIe première génération (versions 1.0 et 1.1). Sur les micro-ordinateurs, nous distinguons des ports PCIe x1, x2, x4, x8, x16 et x32 pour différencier les ports en fonction du nombres de connecteurs de lignes dont il dispose i. e. 1, 2, 4, 8, 16 et 32 lignes , respectivement. De ce fait, un port x32 permet d'atteindre un débit de 8 Go/s, soit 4 fois le débit des ports AGP. 2007 a vu la naissance de la deuxième génération du PCIe. Cette version (PCIe 2.0 et PCIe 2.1) permet d'atteindre un débit de 500 Mo/s par ligne et par sens. Ce qui représente le double du débit de la première génération. Enfin, la troisième version (PCIe 3.0) devrait être commercialisée dès le deuxième semestre 2010 pour atteindre un débit de 1Go/ par ligne et par sens.

### II.1 Anciens bus

Tableau 1 Caractéristiques des anciens bus

| Type    | Largeur bits | Fréquence MHz | Débit Mo/s | Nombre max de connecteurs et configuration des cartes d'extension |                           |

|---------|--------------|---------------|------------|-------------------------------------------------------------------|---------------------------|

| ISA     | 8-16         | 8-12.5        | 8          | 8                                                                 | Configuration matérielle  |

| EISA    | 8-16-32      | 8-12.5-20     | 50         | 18                                                                | Configuration logicielle  |

| MCA     | 16-32        | 8-12.5        | 50         | 8                                                                 | Configuration logicielle  |

| VLB     | 16-32        | 33            | 132        | 3                                                                 | Configuration Plug & Play |

| PCI 1.0 | 16-32        | 33            | 132        | 10                                                                | Configuration Plug & Play |

- ISA** : Industry Standard Architecture.

**EISA** : Extended ISA.

**MCA** : Micro Channel Architecture.

**VLB** : VESA (Video Electronic Standard Association) Local bus.

**PCI** : Peripheral Component Interconnect.

## II.2 Nouveaux bus

Tableau 2 Caractéristiques des nouveaux bus

| Type                                              | Débit max Mo/s    | Max de périphs. | Utilisation                                                |

|---------------------------------------------------|-------------------|-----------------|------------------------------------------------------------|

| <b>PCI 2.0<br/>64 bits</b>                        | 132               | 10              | Compatible EISA,<br>Plug & Play (pont mémoire PCI, ...)    |

| <b>PCI-X 2.0<br/>64 bits</b>                      | 4264              | 10              | Compatible EISA,<br>Plug & Play (pont mémoire PCI, ...)    |

| <b>PCMCIA</b>                                     | 150               | 1               | Cartes à mémoires flash, modems & DD (portables)           |

| <b>DMA/33/66/100/133</b>                          | 33/66/100/133     | 4               | Disque Dur IDE                                             |

| <b>UDMA/33/66/100/133</b>                         | 33/66/100/133     | 4               | Disques Durs ATA et UATA                                   |

| <b>USB 1.0 et 1.1</b>                             | 1.5 Haute Vitesse | 127             | Périphériques Plug & Play à faible débit                   |

| <b>USB 2.0</b>                                    | 60                | -               | Périphériques Plug & Play à haut débit                     |

| <b>USB 3.0</b>                                    | 400               | -               | Périphériques Plug & Play à très haut débit (Disques durs) |

| <b>Fire Wire IEEE 1394</b>                        | 50-400            | 63              | Périphériques rapides (Vidéo numérique)                    |

| <b>AGP 1X/2X/4X/8X</b>                            | 266/533/1000/2000 | 1               | Cartes graphiques ultra rapides                            |

| <b>PCI Express<br/>PCIe 1.0 et 1.1<br/>(2004)</b> | *250              | **              | Cartes graphiques, cartes mémoires, Compact flash, etc.    |

| <b>PCI Express<br/>PCIe 2.0 et 2.1<br/>(2007)</b> | *500              | **              | Cartes graphiques, cartes mémoires, Compact flash, etc.    |

| <b>PCI Express<br/>PCIe 3.0<br/>(2010)</b>        | *1000             | **              | Cartes graphiques, cartes mémoires, Compact flash, etc.    |

\* Débit par ligne et par sens.

\*\* Dépend du slot existant, i.e. x1, x2, x4, x8, x16 ou x32 et de la carte d'extension utilisée.

- PCI-X** : PCI-SIG (Special Interests Group).

**PCMCIA** : Personal Computer Memory Card International Association.

**UDMA** : Ultra Direct Memory Access.

**USB** : Universal Serial Bus.

**IEEE** : Institute of Electrical & Electronics Engineering.

**AGP** : Accelerated Graphic Port.

### **III Evolution des iAPX86**

Avec l'évolution de la gravure, nous ne pouvions que penser à de nouvelles technologies telles que celles du superscalaire, superpipeline, MMX (Multi Media eXtension), MCPU (Multi Central Processing Unit) et MFPU (Multi Floating Processing Unit), de mémoires caches niveaux 1, 2 et 3 intégrées,...

De 2000 à 2004, Pentium, le processeur emblématique de la famille Intel est né avec ses différentes versions II, III et IV. C'est un processeur qui fonctionne en technologie EPIC (Explicitly Parallel Computing). En effet, alors que le pentium II dispose de 2 CPU accompagnés de 8 registres et d'une unité FPU également accompagnées de 8 registres, le Pentium III à 1GHz dispose de plein de CPU associés à 128 registres et plusieurs FPU utilisant également 128 registres. Enfin, les Pentium IV et Prescott sont montés en fréquence (2.8 GHz et 4 GHz) atteignant ainsi un taux de gravure de 0,09µm.

Grâce à la technologie multi core (multi cœur), le dernier lustre a également vu la naissance de processeurs 64 bits très puissants tels que le Core 2 Duo, Core 2 Quad, Core i3, Core i5, Core i7 et le Sandy Bridge dont la technologie est SSE5 (Steraming SIMD Single Instruction on Multiple Data Extension version, par opposition au fonctionnement du jeu d'instructions traditionnel, i.e., SISD: Single Instruction Single Data). Ces processeurs à très faible consommation d'énergie sont passés à des modes de fonctionnement très complexes tel que celui du 'out-of-order' qui exalte les plus grands acteurs de l'informatique. La loi Moore ne veut pas s'arrêter en si bon chemin. Elle compte aller jusqu'à 2014 pour atteindre une gravure de 6nm i.e. taux d'intégration au-delà de 1 G transistors et des performances excédant 1 GIPS, voire même au delà. Le Tableau 3 synthétise la chronologie des différentes architectures de microprocesseurs et coprocesseurs de la firme Intel.

Tableau 3 Différentes architectures des microprocesseurs Intel

| Architecture                 | Microprocesseur/Coprocesseur                                                                               |

|------------------------------|------------------------------------------------------------------------------------------------------------|

| Pre-x86                      | 4004 - 4040 - 8008 - 8080 - 8085                                                                           |

| x86-16                       | 8086 - 8088 - 80186 - 80188 - 80286                                                                        |

| X87 (ext. FPU)               | 8087 (8/16) - 80287 (16) - 80387 - 80487 (32)                                                              |

| X86-32/IA-32                 | 80386 - 80486 (SX-DX2-DX4-SL) - Pentium (Original - Pro - II - III - 4 - M) - Core - Celeron M - Celeron D |

| X86-64/EM64                  | Pentium 4 - Pentium D - Pentium Extreme - Celeron D                                                        |

| Core-based Microarchitecture | Core Solo - Core Duo - Core 2 Duo - Core 2 Quad - Core i3 - Core i5 - Core i7                              |

FPU : Floating Point Unit.

### III.1 Microprocesseurs

| Trans.        | 1975 | 1980  | 1985  | 1990    | 1995           | 2000         | 2005          | 2010   | MIPS   |

|---------------|------|-------|-------|---------|----------------|--------------|---------------|--------|--------|

| 1000 M        |      |       |       |         |                |              |               | Core i | 150000 |

| 100 M         |      |       |       |         |                |              | Prescott P IV | Core 2 | 50000  |

| 10 M          |      |       |       |         | P Pro<br>P MMX | P III<br>PII |               |        | 1000   |

| 1 M           |      |       | 80486 | Pentium |                |              |               |        | 500    |

| 300K<br>140 K |      | 80286 | 80386 |         |                |              |               |        | 100    |

| 30 K          | 8086 |       |       |         |                |              |               |        | 25     |

| 6.K           | 8085 |       |       |         |                |              |               |        | 1      |

| 2.3 K         | 4004 |       |       |         |                |              |               |        | 0.5    |

|               |      |       |       |         |                |              |               |        | 0.4    |

|               |      |       |       |         |                |              |               |        | 0.06   |

Fig. 1 Evolution des microprocesseurs Intel

Le Tableau 4 illustre quelques exemples du parc microprocesseurs Intel, partant de la plus de la deuxième génération (80286) à la onzième génération (Sandy Bridge).

Tableau 4 Caractéristiques de quelques microprocesseurs Intel (Ancienne et nouvelle générations)

| Type                    | An.<br>Fab. | Fréq.<br>MHz                                                                               | Bus<br>@<br>(bits) | Bus<br>Data<br>(bits) | Cache<br>L <sub>1</sub><br>(KO) | Cache<br>L <sub>2</sub><br>(KO) | Alim.<br>(V) |

|-------------------------|-------------|--------------------------------------------------------------------------------------------|--------------------|-----------------------|---------------------------------|---------------------------------|--------------|

| <b>286</b>              | 1982        | 8-20                                                                                       | 24                 | 16                    | -                               | -                               | 5            |

| <b>386DX</b>            | 1985        | 16-33                                                                                      | 32                 | 32                    | -                               | -                               | 5            |

| <b>486DX</b>            | 1989        | 33-100                                                                                     | 32                 | 32                    | 8                               | Ext.                            | 5 - 3.3      |

| <b>Pent.</b>            | 1993        | 60-200                                                                                     | 32                 | 2 x 32                | 2 x 8                           | Ext.                            | 3.3 - 2.9    |

| <b>P MMX</b>            | 1995        | 200-266                                                                                    | 32                 | 2 x 32                | 2 x 16                          | Ext.                            | 2.8          |

| <b>P Pro.</b>           | 1995        | 150-200                                                                                    | 32                 | 2 x 32                | 2 x 8                           | 256                             | 3.1 - 2.9    |

| <b>P II</b>             | 1997        | 266-450                                                                                    | 32                 | 2 x 32                | 2 x 8                           | 256                             | 2.8          |

| <b>P III</b>            | 1999        | 450-1000                                                                                   | 32                 | 32                    | 2 x 16                          | 512                             | 2.8          |

| <b>P 4</b>              | 2002        | 1300-2800                                                                                  | 32                 | 32                    | 2 x 16                          | 512                             | 2.8          |

| <b>Prescott</b>         | 2004        | 3400-4000                                                                                  | 32                 | 32                    | 16                              | 2048                            | 2.8          |

| <b>*Core 2</b>          | 2006        | 1860-3200                                                                                  | 32                 | 64                    | 64                              | 4096                            | 1 - 1.15     |

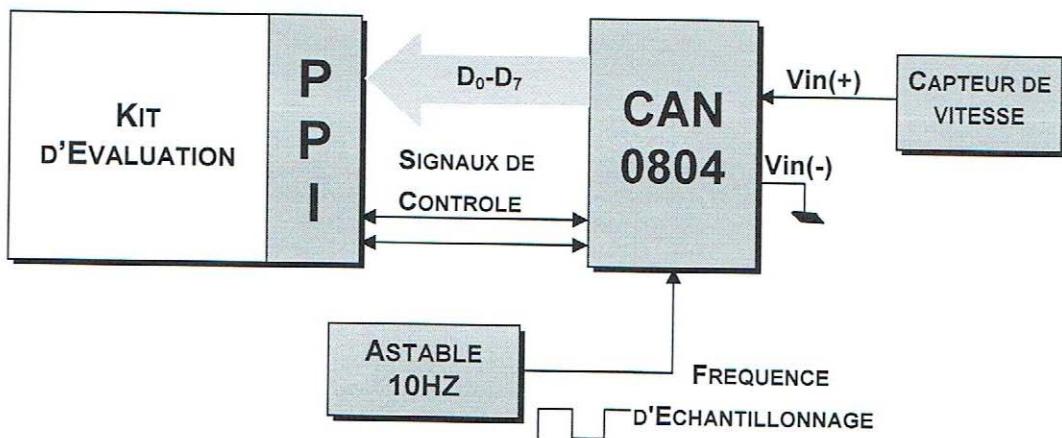

| <b>*Core i</b>          | 2008        | 2600-3600                                                                                  | 48                 | 64                    | 64                              | 512                             | 1.2 - 1.3    |